Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Programa de Pós-Graduação em Engenharia Elétrica

## AC-DC-AC Power Conversion Systems for Applications as Unified Power Quality Conditioners.

Jean Torelli Cardoso

Campina Grande - PB, Brasil August 2024

Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Programa de Pós-Graduação em Engenharia Elétrica

## AC-DC-AC Power Conversion Systems for Applications as Unified Power Quality Conditioners.

Jean Torelli Cardoso

Doctoral Dissertation submitted to the Coordenação do Curso de Pós-Graduação em Engenharia Elétrica from Universidade Federal de Campina Grande, as part of the requirements for obtaining the degree of D.Sc. in Electrical Engineering.

Concentration area: Energy Processing

Supervisor: Prof. Dr. Ing. Cursino Brandão Jacobina Campina Grande - PB, Brasil August 2024

C268a Cardoso, Jean Torelli. AC-DC-AC power conversion systems for applications as unified power quality conditioners / Jean Torelli Cardoso – Campina Grande, 2024. 230 f. : il. color.

Tese (Doutorado em Engenharia Elétrica) – Universidade Federal de Campina Grande, Centro de Engenharia Elétrica e Informática, 2024. "Orientação: Prof. Dr. Cursino Brandão Jacobina". Referências.

1. Multilevel Converter. 2. High-Frequency Link. 3. UPQC System. 4. Power Quality. I. Jacobina, Cursino Brandão. II. Título.

FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECÁRIA MEIRE EMANUELA DA SILVA MELO CRB-15/568

AC-DC-AC Power Conversion Systems for Applications as Unified Power Quality Conditioners

JEAN TORELLI CARDOSO

TESE APROVADA EM 29/08/2024

### CURSINO BRANDÃO JACOBINA, Dr.Ing., UFCG Orientador(a)

### ANTONIO MARCUS NOGUEIRA LIMA, Dr., UFCG Examinador(a)

### ALEXANDRE CUNHA OLIVEIRA, D.Sc., UFCG Examinador(a)

### LEONARDO RODRIGUES LIMONGI, Dr., UFPE Examinador(a)

### LUIZ HENRIQUE SILVA COLADO BARRETO, Dr., UFC Examinador(a)

### **CAMPINA GRANDE - PB**

SEI/UFCG - 4751765 - Ata de Defesa

MINISTÉRIO DA EDUCAÇÃO UNIVERSIDADE FEDERAL DE CAMPINA GRANDE POS-GRADUACAO EM ENGENHARIA ELETRICA Rua Aprigio Veloso, 882, - Bairro Universitario, Campina Grande/PB, CEP 58429-900

### **REGISTRO DE PRESENÇA E ASSINATURAS**

# 1. ATA DA DEFESA PARA CONCESSÃO DO GRAU DE DOUTOR EM CIÊNCIAS, NO DOMÍNIO DA ENGENHARIA ELÉTRICA, REALIZADA EM 29 DE AGOSTO DE 2024

(Nº 381)

CANDIDATO(A): JEAN TORELLI CARDOSO. COMISSÃO EXAMINADORA: ANTONIO MARCUS NOGUEIRA LIMA, Dr., UFCG - Presidente da Comissão e Examinador Interno, CURSINO BRANDÃO JACOBINA, Dr. Ing., UFCG, Orientador, ALEXANDRE CUNHA OLIVEIRA, D.Sc., UFCG - Examinador Interno, LEONARDO RODRIGUES LIMONGI, Dr., UFPE - Examinador Externo, LUIZ HENRIQUE SILVA COLADO BARRETO, Dr., UFC - Examinador Externo TÍTULO DA TESE: AC-DC-AC Power Conversion Systems for Applications as Unified Power Quality Conditioners. ÁREA DE CONCENTRAÇÃO: Processamento da Energia. HORA DE INÍCIO: 09h00 − LOCAL: Sala Virtual, conforme Art. 5º da PORTARIA SEI № 01/PRPG/UFCG/GPR, DE 09 DE MAIO DE 2022. Em sessão pública, após exposição de cerca de 45 minutos, o(a) candidato(a) foi arguido(a) oralmente pelos membros da Comissão Examinadora, tendo demonstrado suficiência de conhecimento e capacidade de sistematização, no tema de sua tese, obtendo conceito APROVADO. Face à aprovação, declara o presidente da Comissão, achar-se o examinado, legalmente habilitado a receber o Grau de Doutor em Ciências, no domínio da Engenharia Elétrica, cabendo a Universidade Federal de Campina Grande, como de direito, providenciar a expedição do Diploma, a que o(a) mesmo(a) faz jus. Na forma regulamentar, foi lavrada a presente ata, que é assinada por mim, Leandro Ferreira de Lima, e os membros da Comissão Examinadora. Campina Grande, 29 de Agosto de 2024.

> LEANDRO FERREIRA DE LIMA Secretário

ANTONIO MARCUS NOGUEIRA LIMA, Dr., UFCG Presidente da Comissão e Examinador Interno

CURSINO BRANDÃO JACOBINA, Dr.Ing., UFCG Orientador

#### SEI/UFCG - 4751765 - Ata de Defesa

### ALEXANDRE CUNHA OLIVEIRA, D.Sc., UFCG Examinador Interno

### LEONARDO RODRIGUES LIMONGI, Dr., UFPE Examinador Externo

#### LUIZ HENRIQUE SILVA COLADO BARRETO, Dr., UFC

#### Examinador Externo

#### JEAN TORELLI CARDOSO

#### Candidato

#### 2 - APROVAÇÃO

2.1. Segue a presente Ata de Defesa de Tese de Doutorado da candidato **JEAN TORELLI CARDOSO**, assinada eletronicamente pela Comissão Examinadora acima identificada.

2.2. No caso de examinadores externos que não possuam credenciamento de usuário externo ativo no SEI, para igual assinatura eletrônica, os examinadores internos signatários **certificam** que os examinadores externos acima identificados participaram da defesa da tese e tomaram conhecimento do teor deste documento.

Documento assinado eletronicamente por **LEANDRO FERREIRA DE LIMA**, **SECRETÁRIO (A)**, em 30/08/2024, às 09:42, conforme horário oficial de Brasília, com fundamento no art. 8º, caput, da <u>Portaria SEI nº 002, de 25 de outubro de 2018</u>.

Documento assinado eletronicamente por **Luiz Henrique Silva Colado Barreto**, **Usuário Externo**, em 30/08/2024, às 09:53, conforme horário oficial de Brasília, com fundamento no art. 8º, caput, da <u>Portaria SEI nº 002, de 25 de outubro de 2018</u>.

Documento assinado eletronicamente por **ALEXANDRE CUNHA OLIVEIRA**, **PROFESSOR 3 GRAU**, em 30/08/2024, às 10:19, conforme horário oficial de Brasília, com fundamento no art. 8º, caput, da <u>Portaria SEI nº 002, de 25 de outubro de 2018</u>.

Documento assinado eletronicamente por **ANTONIO MARCUS NOGUEIRA LIMA**, **PROFESSOR(A) DO MAGISTERIO SUPERIOR**, em 30/08/2024, às 10:28, conforme horário oficial de Brasília, com fundamento no art. 8º, caput, da <u>Portaria SEI nº 002, de 25 de outubro de 2018</u>.

Documento assinado eletronicamente por **CURSINO BRANDAO JACOBINA**, **PROFESSOR 3 GRAU**, em 31/08/2024, às 13:42, conforme horário oficial de Brasília, com fundamento no art. 8º, caput, da <u>Portaria SEI nº 002, de 25 de outubro de 2018</u>.

Documento assinado eletronicamente por **Jean Torelli Cardoso**, **Usuário Externo**, em 02/09/2024, às 09:22, conforme horário oficial de Brasília, com fundamento no art. 8º, caput, da <u>Portaria SEI nº 002,</u> <u>de 25 de outubro de 2018</u>.

## Resumo

Neste trabalho, são analisadas seis configurações ca-cc-ca monofásicas e duas trifásicas que podem operar com melhores níveis de distorção harmônica e eficiência que topologias convencionais dentro de alguns cenários de aplicações. Nesse sentido, esse trabalho teve como objetivos: i) propor e analisar configurações cacc-ca monofásicas com características multiníveis, ou seja, que possam sintetizar formas de onda multiníveis e menores tensões de bloqueio nos dispositivos semicondutores; *ii*) propor e analisar configurações ca-cc-ca monofásicas, assim como, estratégias de controle que permitam melhorar a performance da estrtura em termos de tensão mínima no barramento CC e compensação série; *iii*) propor e analisar configurações ca-cc-ca trifásicas multiníveis a quatro fios que permitam alcançar melhores desempenhos em termos de tensão mínima no barramento ao operar com cargas severamente desbalaceadas. Os conversores ca-cc-ca monofásicos e trifásicos analisados fornecem uma tensão de saída com amplitude e frequência constantes, além de uma corrente de entrada senoidal com baixo teor harmônico e elevado fator de potência. Além disso, estes conversores estudados podem ser empregados para compensar harmônicos, sobretensões e afundamentos na tensão da rede elétrica, bem como para corrigir a potência reativa e reduzir os harmônicos gerados por cargas não lineares. A metodologia de estudo dessas configurações envolve uma análise detalhada das configurações investigadas, incluindo o modelo do sistema, princípios de operação, estratégia de modulação PWM (do inglês, Pulse Width Modulation) e estratégia de controle. A validação das configurações estudadas de forma a verificar a viabiliade, foram realizadas por meio de simulações numéricas e resultados experimentais. Adicionalmente, foram feitas análises comparativas em relação as configurações convencionais e pôde-se verificar benefícios em termos de distorção harmônica e perdas nos dispositivos semicondutores, sobretudo, em cenários de tensão elevada e baixa corrente. As configurações propostas podem ser utilizadas como Condicionadores Unificados de Qualidade de Energia (UPQC, do inglês Unified Power Quality Conditioner).

**Palavras-chave:** Conversor Multinível, Link de Alta Frequência, Sistemas UPQC, Qualidade de Energia.

## Abstract

In this work, six single-phase and two three-phase ac-dc-ac configurations that can operate with better levels of harmonic distortion and efficiency than conventional solutions within some application scenarios are analyzed. In this context, this work had the following objectives: i) to propose and analyze ac-dc-ac configurations with multilevel characteristics, that is, that can synthesize multilevel waveforms and lower blocking voltages in semiconductor devices; *ii*) to propose and analyze single-phase ac-dc-ac configurations, as well as control strategies that improve the performance of the structure in terms of minimum dc-link voltage and series compensation; *iii*) to propose and analyze three-phase four wire multilevel ac-dc-ac configurations that achieve better performance in terms of minimum dc-link voltage when operating with severely unbalanced loads. The analyzed single-phase and three-phase converters are able to provide a load voltage with constant amplitude and frequency, as well as a sinusoidal grid current with low harmonic content and a high power factor. Furthermore, the studied converters can be used to compensate for harmonics, swells, and sags in the grid voltage, as well as to compensate reactive power and reduce harmonics caused by nonlinear loads. The study methodology for these configurations involves a detailed analysis of the proposed configurations, including the system model, operating principles, PWM modulation strategy, and control strategy. The validation of the studied configurations, to verify their feasibility, was conducted through numerical simulations and experimental results. Additionally, comparative analyses were performed against conventional configurations, demonstrating benefits in terms of harmonic distortion and losses in semiconductor devices, particularly in scenarios of high voltage and low current. The studied configurations can be used as Unified Power Quality Conditioners (UPQC).

**Keywords:** Multilevel Converter, High-Frequency Link, UPQC System, Power Quality.

# List of Tables

| Table 1.1 | –Classification of short-term voltage variations according to ANEEL -                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Procedimentos de Distribuição de Energia Elétrica no Sistema Elétrico                                                                                                             |

|           | Nacional (PRODIST), Módulo 8 – Qualidade de Energia Elétrica 3                                                                                                                    |

| Table 1.2 | –Classification of short-term voltage variations according to IEEE 1159-                                                                                                          |

|           | 1995 - "IEEE Recommended Practice for Monitoring Electrical Power                                                                                                                 |

|           | Quality"                                                                                                                                                                          |

| Table 2.1 | -Transformer turn ratios, levels of $v_g$ and $v_l$ , and range of $\theta_{lg}$                                                                                                  |

| Table 2.2 | –Sequences of vectors applied for $\eta = 1, 2, \text{ and } 3$ to minimize the switching                                                                                         |

|           | losses                                                                                                                                                                            |

| Table 2.3 | –Parameters Considered For Tests                                                                                                                                                  |

| Table 2.4 | -Capacitor-current contribution in $E_a$                                                                                                                                          |

| Table 2.5 | -Parameters used in simulations and experimental tests                                                                                                                            |

| Table 2.6 | –Parameters of The HFT used in simulations and experimental tests $39$                                                                                                            |

| Table 2.7 | –Voltage WTHD (%) and current THD (%) values                                                                                                                                      |

| Table 2.8 | -Power Losses Evaluation for $\text{THD}(i_g) = 5\%$                                                                                                                              |

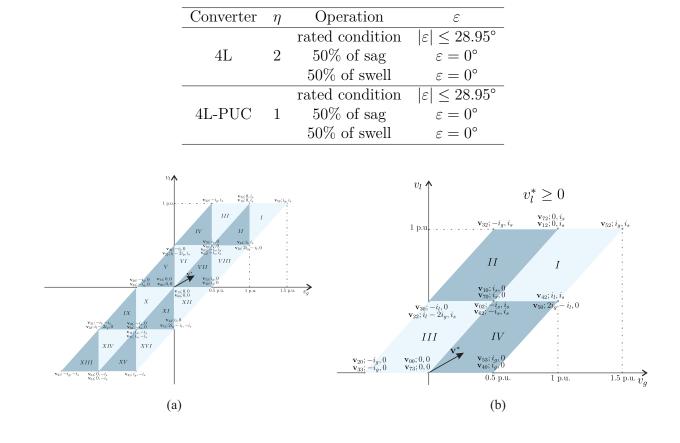

| Table 3.1 | –Characteristics of 4L and 4L-PUC Configurations According To the                                                                                                                 |

|           | Transformer Turn Ratio                                                                                                                                                            |

| Table 3.2 | –Phase Angle Limits Between $v_g$ and $v_l$                                                                                                                                       |

| Table 3.3 | –Selected vector sequences and calculated reference pole voltage to charge                                                                                                        |

|           | or discharge dc-link voltage $E_a$ for $\eta = 1. \ldots $ |

| Table 3.4 | –Parameters used in simulations and experimental tests                                                                                                                            |

| Table 3.5 | -Experimental efficiency values for 4L-PUC and 4L                                                                                                                                 |

| Table 3.6 | -Parameters considered for the tests                                                                                                                                              |

| Table 3.7 | -Rating of the semiconductor devices                                                                                                                                              |

| Table 3.8 | –Voltage WTHD and current THD analysis                                                                                                                                            |

| Table 3.9 | -Semiconductor power losses                                                                                                                                                       |

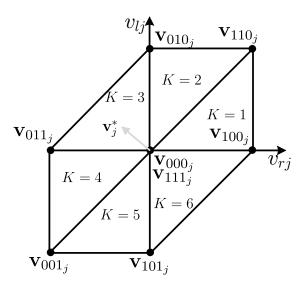

| Table 4.1 | –Detailing the voltage vectors in plane and the vector sequence applied                                                                                                           |

|           | for each sector. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.99$                                                                                    |

| Table 4.2 | –Parameters used in simulations and experimental tests. $\ldots \ldots \ldots \ldots 104$                                                                                         |

| Table 4.3 | –Parameters used in simulations and experimental tests. $\ldots$ $\ldots$ $\ldots$ 118                                                                                            |

| Table 4.4 | –Parameters used in simulations and experimental tests                                                                                                                            |

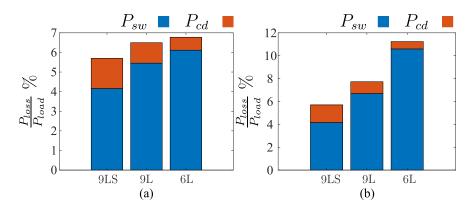

| Table 4.5 | –Parameters considered for the tests                                                                                                                                              |

| Table 4.6 | -Rating of the semiconductor devices                                                                                                                                              |

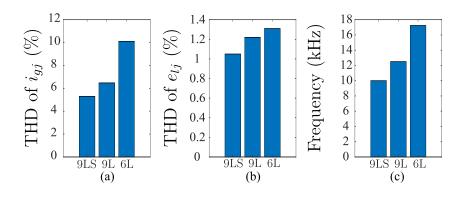

| Table 4.7 | -THD analysis                                                                                                                                                                     |

| Table 4.8 -Semiconductor power losses.    148                                         |

|---------------------------------------------------------------------------------------|

| Table 5.1 -Parameters used in simulations and experimental tests.                     |

| Table 5.2 -Parameters considered for the tests.    165                                |

| Table 5.3 - Rating of the semiconductor devices.    166                               |

| Table 5.4 –THD analysis                                                               |

| Table 5.5 –Semiconductor power losses - 0.5 kW - 110V                                 |

| Table 5.6 –Semiconductor power losses - 1 kW - 110V                                   |

| Table 5.7 –Semiconductor power losses - 2 kW - 110V                                   |

| Table 5.8 –Semiconductor power losses - 0.5 kW - 220V                                 |

| Table 5.9 –Semiconductor power losses - 1 kW - 220V                                   |

| Table 5.10 $-$ Semiconductor power losses - 2 kW - 220V                               |

| Table 6.1 -Parameters used in the tests.    180                                       |

| Table 6.2 - Parameters used in comparative analysis.    11                            |

| Table 7.1 $-$ Location of the triangular sectors of the SVPWM, calculation of duty-   |

| cycles and resulting vector sequence                                                  |

| Table 7.2 $$ –Parameters considered for simulation and experimental results $$ 204 $$ |

| Table 7.3 –Comparison of overall features with some available UPQCs. ( $E_g = 1$ p.u. |

| = 155.56  V)                                                                          |

Table 8.1  $\,$  –Comparison of overall features with some available transformer less UPQCs.216  $\,$

# List of Figures

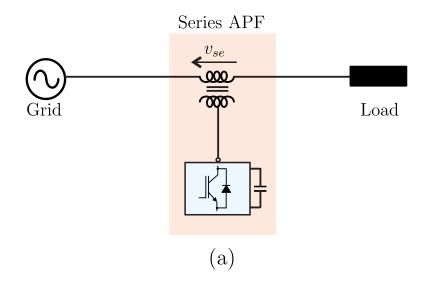

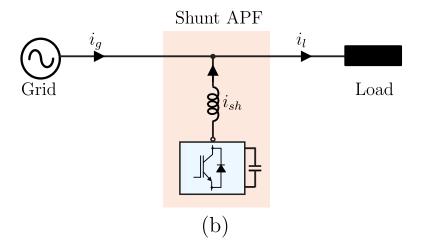

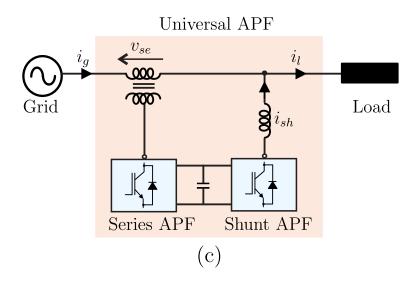

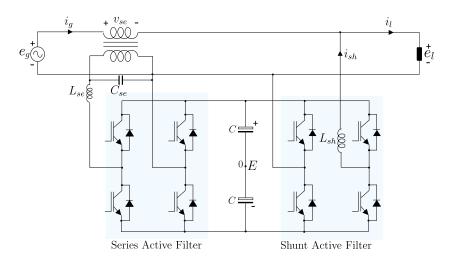

| Figure 1.1  | –Power quality devices. (a) Series APF. (B) Shunt APF. (c) Universal          |    |

|-------------|-------------------------------------------------------------------------------|----|

|             | APF                                                                           | 5  |

| Figure 1.2  | –Conventional ac-dc-ac converter (MORAN, 1989)                                | 6  |

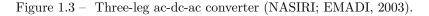

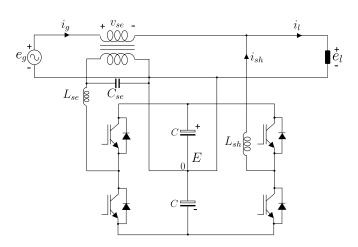

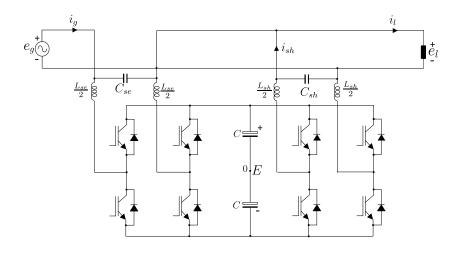

| Figure 1.3  | -Three-leg ac-dc-ac converter (NASIRI; EMADI, 2003)                           | 7  |

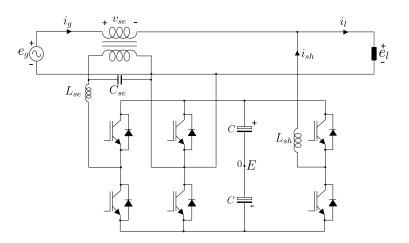

| Figure 1.4  | –Half-bridge ac-dc-ac converter (NASIRI; EMADI, 2003)                         | 7  |

| Figure 1.5  | –Transformerless four-leg ac-dc-ac converter (SANTOS et al., 2014). $$ .      | 8  |

| Figure 1.6  | -Transformerless three-leg ac-dc-ac converter (3L-UPQC) (LU et al., 2016).    | 8  |

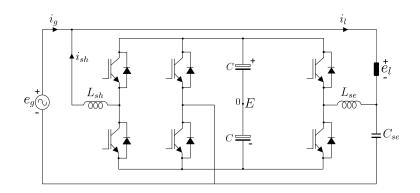

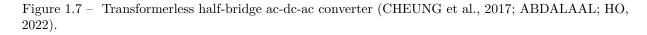

| Figure 1.7  | –Transformerless half-bridge ac-dc-ac converter (CHEUNG et al., 2017;         |    |

|             | ABDALAAL; HO, 2022)                                                           | 9  |

| Figure 1.8  | –Transformerless six-switch two-leg converter (GENU et al., 2020) $1$         | 10 |

| Figure 1.9  | -Four-leg single-phase system based on high-frequency transformer (PEREDA;    | ;  |

|             | DIXON, 2011)                                                                  | 10 |

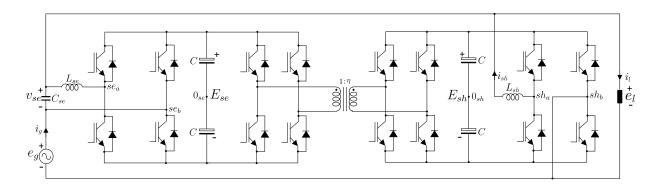

| Figure 1.10 | -Ac-dc-ac six-leg converter (CHANG; CHANG; CHIANG, 2006) 1                    | 11 |

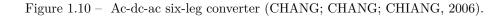

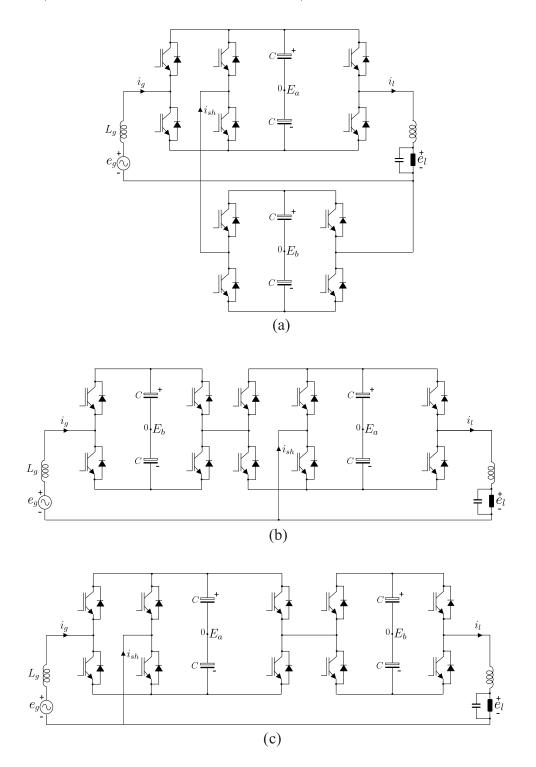

| Figure 1.11 | Single-phase ac-dc-ac five-leg converters. (a) Based on three-leg and         |    |

|             | a h-bridge connected to the common part of the converter (MAIA;               |    |

|             | JACOBINA, 2014). (b) Based on three-leg and a h-bridge connected              |    |

|             | in the grid side (MAIA; JACOBINA, 2017). (c) Based on three-leg               |    |

|             | and a h-bridge connected in the load side (LACERDA; JACOBINA;                 |    |

|             | FABRICIO, 2022)                                                               | 12 |

| Figure 1.12 | -Single-phase ac-dc-ac converter based on NPC leg (FREITAS et al., 2010). $1$ | 13 |

| Figure 1.13 | -Single-phase ac-dc-ac converter based on t-type leg (KWON; KWON;             |    |

|             | KWON, 2018)                                                                   | 13 |

| Figure 1.14 | -Single-phase ac-dc-ac converter based on flying capacitor leg (LIN;          |    |

|             | HUANG, 2004)                                                                  | 14 |

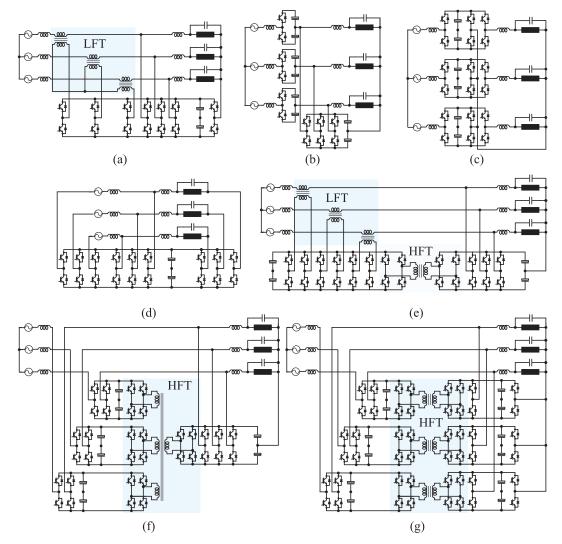

| Figure 1.15 | -UPQC configurations with low-frequency transformers. (a) UPQC con-           |    |

|             | figuration based on six legs with the central point of the dc link used as    |    |

|             | the connection point for the fourth wire. (b) UPQC configuration based        |    |

|             | on seven legs. (c) UPQC configuration based on ten legs with h-bridge         |    |

|             | converters in the series unit                                                 | 15 |

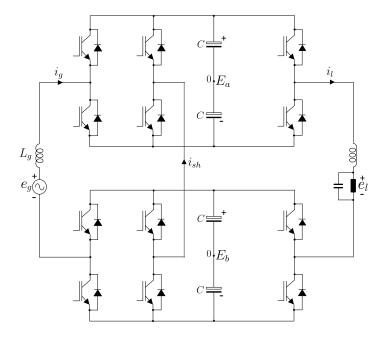

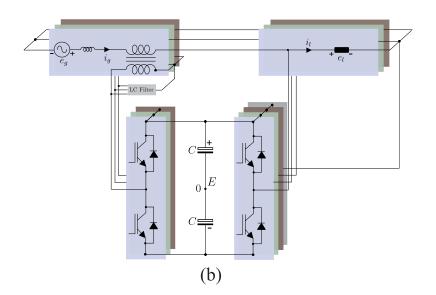

| Figure 1.16 | -Three-phase UPQC configurations without low-frequency transformers.          |    |

|             | (a) UPQC configuration based on six legs with the central point of the        |    |

|             | dc link used as the connection point for the fourth wire. (b) Multilevel      |    |

|             | UPQC configuration based on NPC legs                                          | 17 |

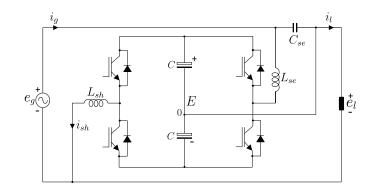

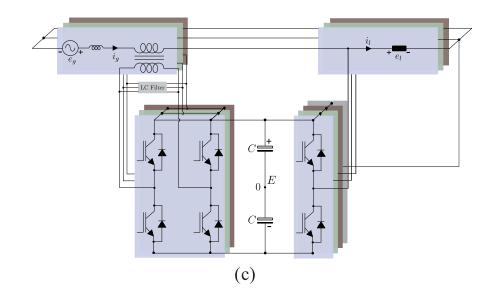

| Figure 1.17 | -Multilevel three-phase UPQC configurations without low-frequency                                 |    |

|-------------|---------------------------------------------------------------------------------------------------|----|

|             | transformers based on single-phase ac-dc-ac modules. (a) Twelve-leg                               |    |

|             | converter based on a full-bridge module per phase. (b) Nine-leg converter                         |    |

|             | based on a three-leg converter per phase                                                          | 18 |

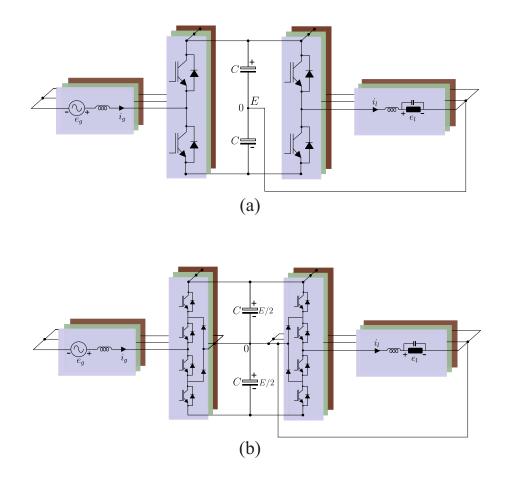

| Figure 1.18 | -Three-phase UPQC configurations without low-frequency transformers                               |    |

|             | based on separate series and shunt units into modules with individualized                         |    |

|             | de links                                                                                          | 19 |

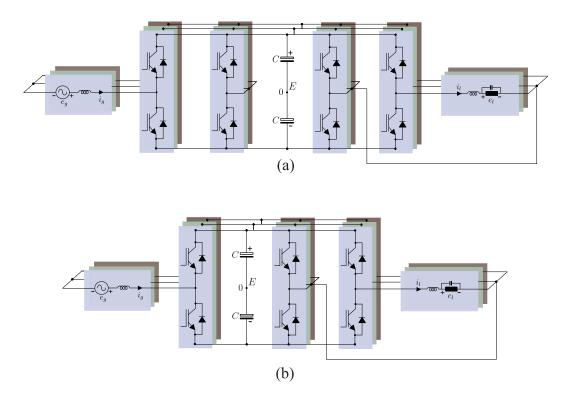

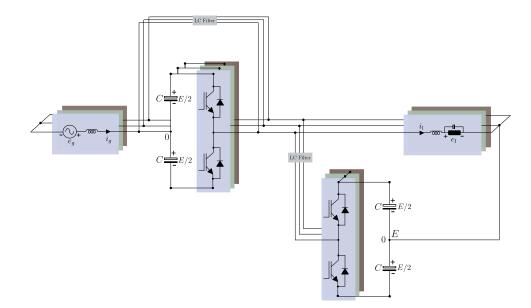

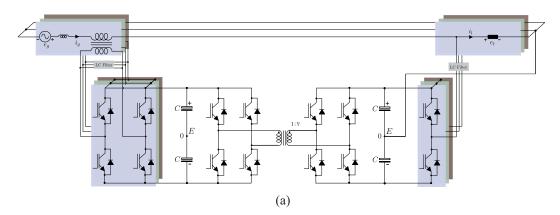

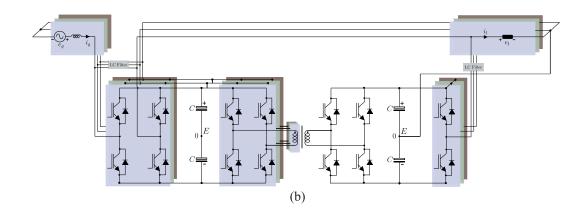

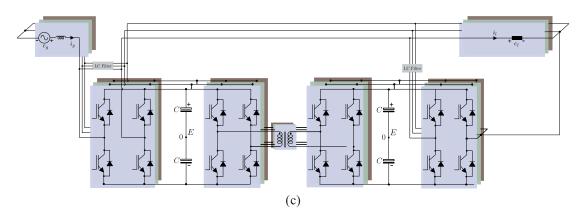

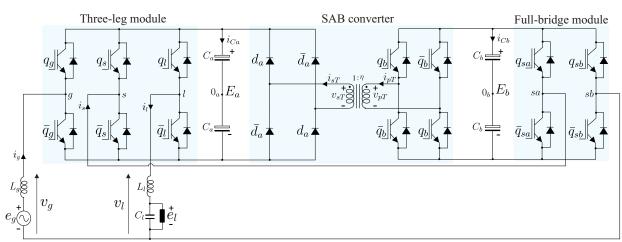

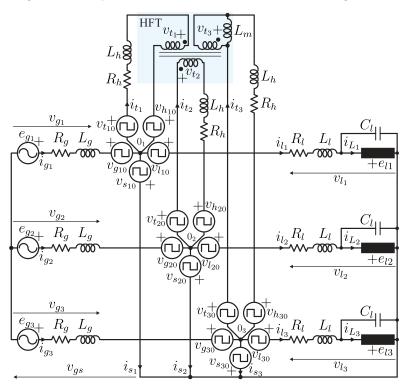

| Figure 1.19 | -Three-phase UPQC configurations based on high-frequency transformers.                            |    |

|             | (a) Three-phase UPQC configuration with fourteen legs. (b) Three-                                 |    |

|             | phase UPQC configuration with eighteen legs. (c) Three-phase UPQC                                 |    |

|             | configuration with twenty four legs                                                               | 19 |

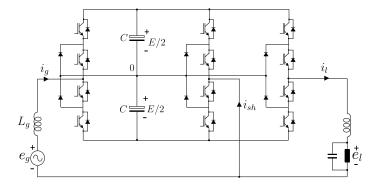

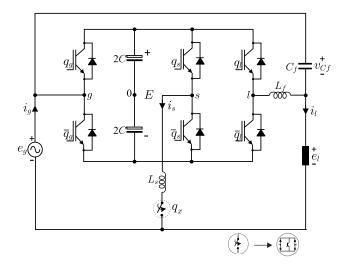

| Figure 1.20 | Proposed five-leg ac-dc-ac converter based on high-frequency transformer.                         | 21 |

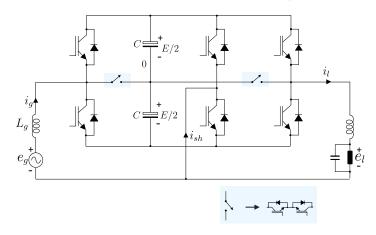

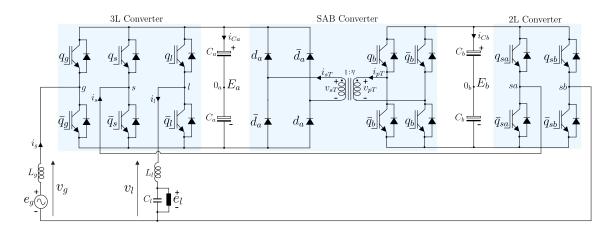

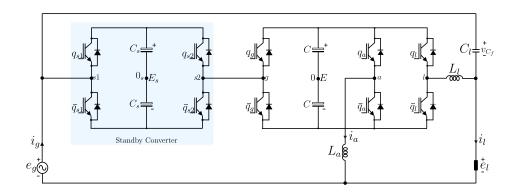

| Figure 1.21 | Proposed ac-dc-ac converter based on PUC converter                                                | 22 |

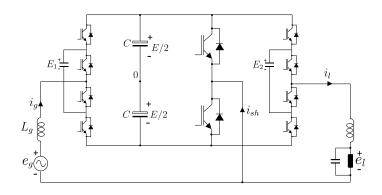

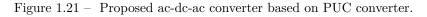

| Figure 1.22 | Proposed transformerless three-leg converter                                                      | 23 |

| Figure 1.23 | -Proposed SB-3LS-UPQC configuration.                                                              | 23 |

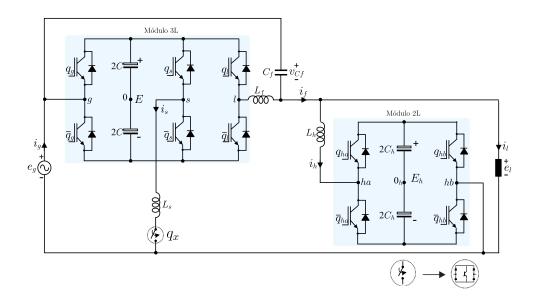

| Figure 1.24 | -Proposed 3LS-SH-UPQC configuration.                                                              | 23 |

| Figure 1.25 | Proposed 4L-UPQC configuration.                                                                   | 24 |

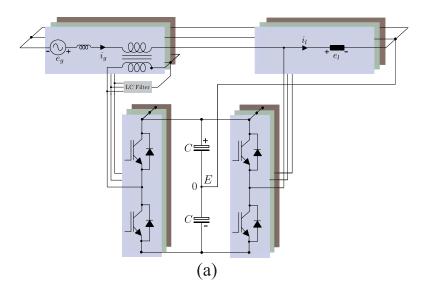

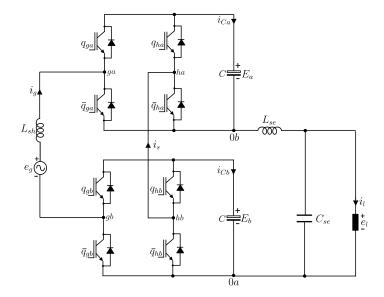

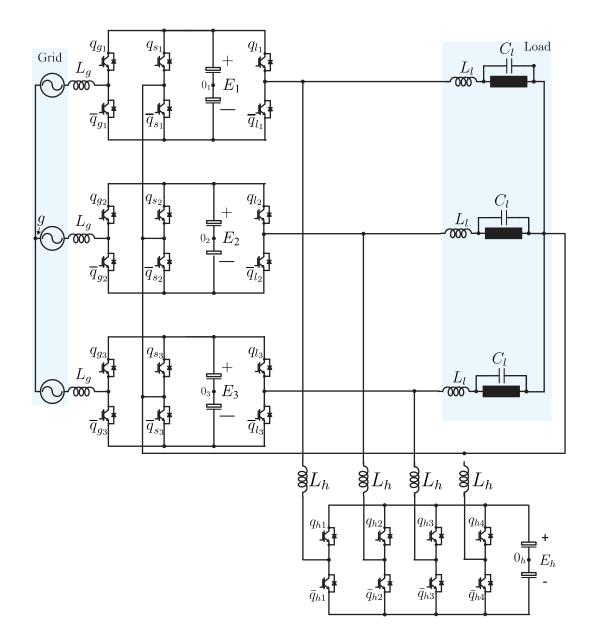

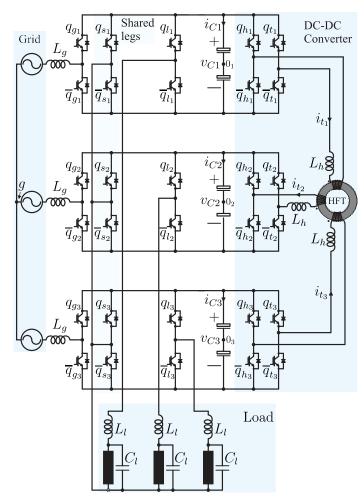

| Figure 1.26 | -Proposed 9LS-UPQC configuration.                                                                 | 25 |

| Figure 1.27 | -9LHF-UPQC configuration.                                                                         | 25 |

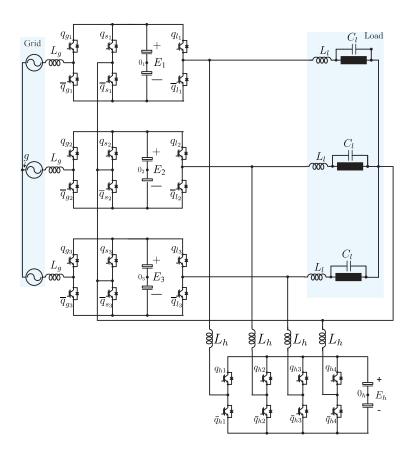

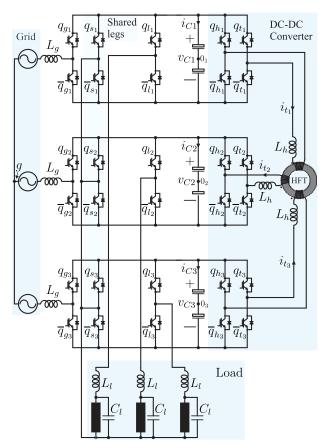

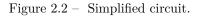

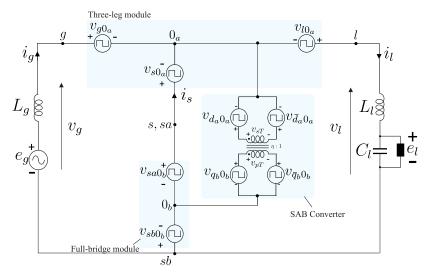

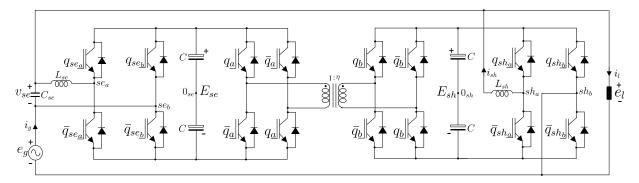

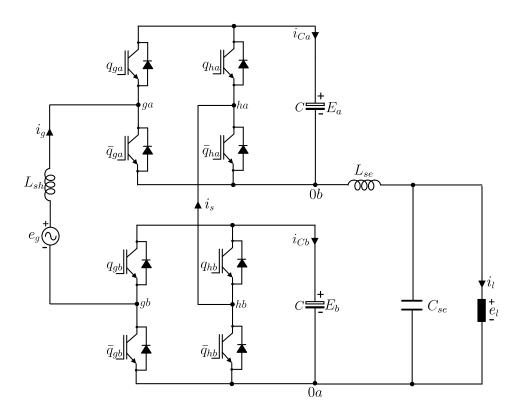

| Figure 2.1  | –Proposed 5L-HFL Converter.                                                                       | 30 |

| Figure 2.2  | -Simplified circuit.                                                                              | 30 |

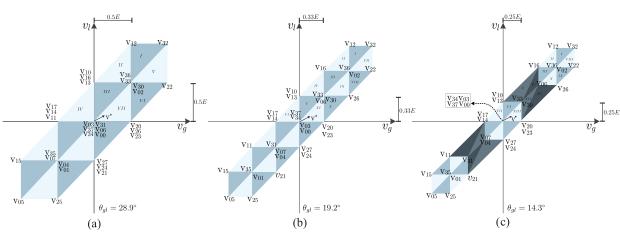

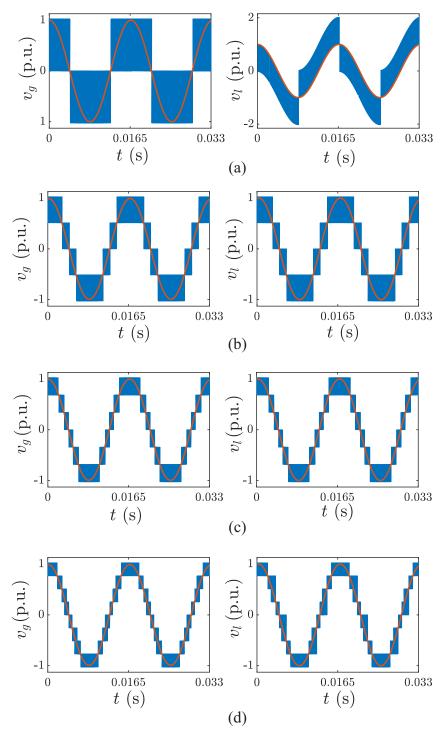

| Figure 2.3  | -Space-vector plans generated by the proposed converter. (a) $E_b = E_a$                          |    |

|             | $(\eta = 1).$ (b) $E_b = 2E_a$ $(\eta = 2).$ (c) $E_b = 3E_a$ $(\eta = 3).$                       | 32 |

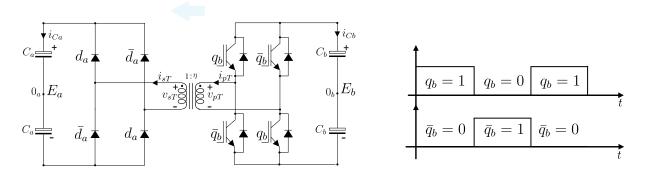

| Figure 2.4  | –Power flow direction in the HFL and switching states                                             | 34 |

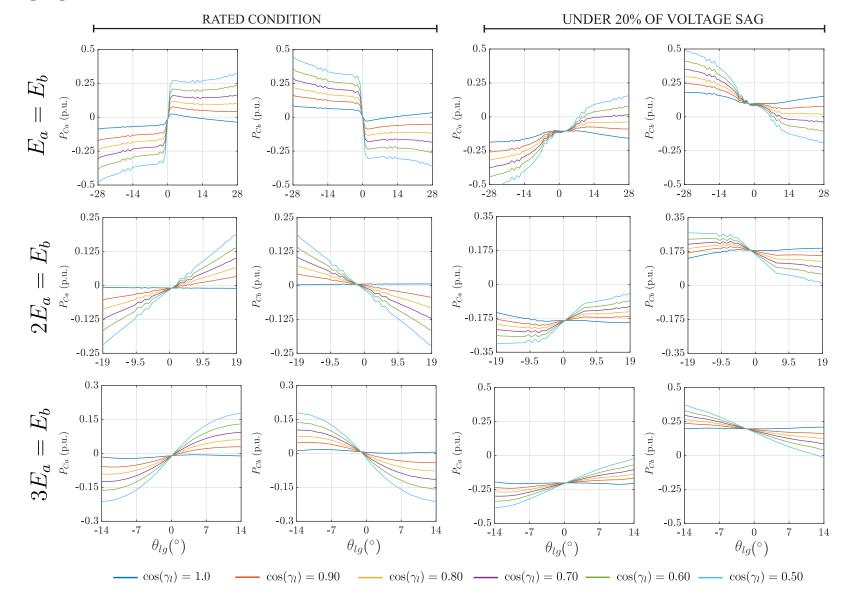

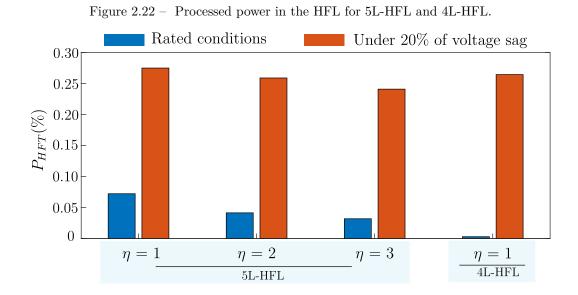

| Figure 2.5  | -Power distribution $P_{Ca}$ and $P_{Cb}$ of dc-links A and B for all transformer                 |    |

|             | ratio cases and considering the operation under rated conditions and                              |    |

|             | under 20% of voltage sag. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 37 |

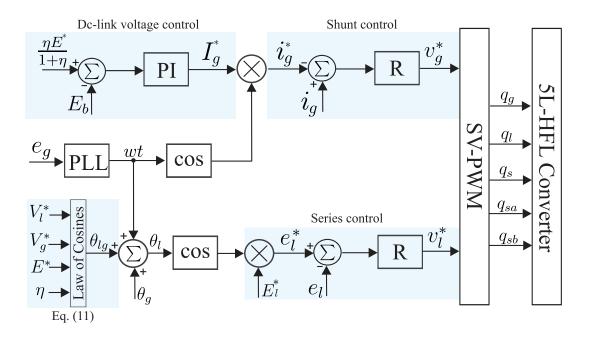

| Figure 2.6  | -Control block diagram.                                                                           | 38 |

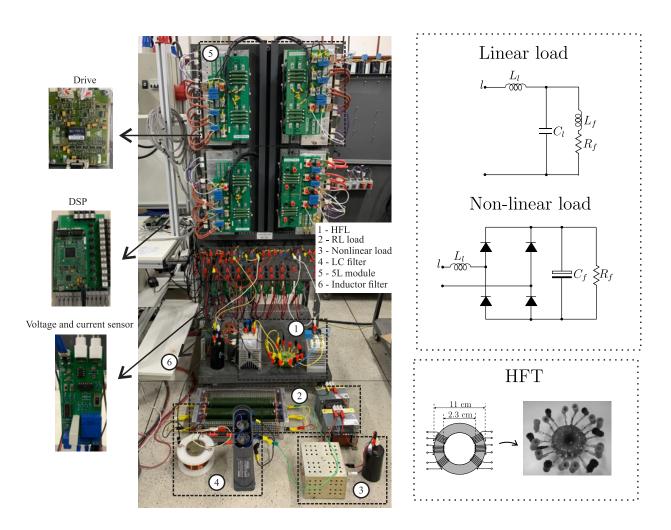

| Figure 2.7  | -Experimental setup for the 5L-HFL converter                                                      | 40 |

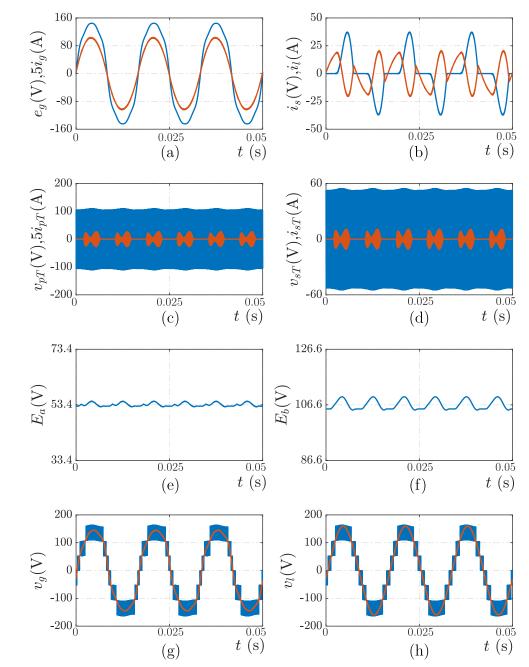

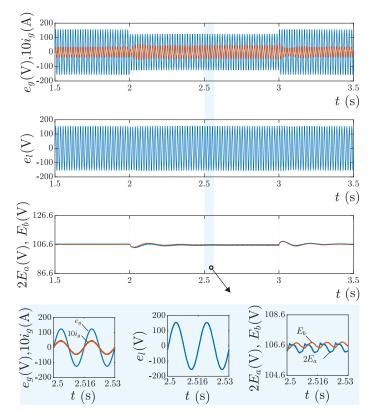

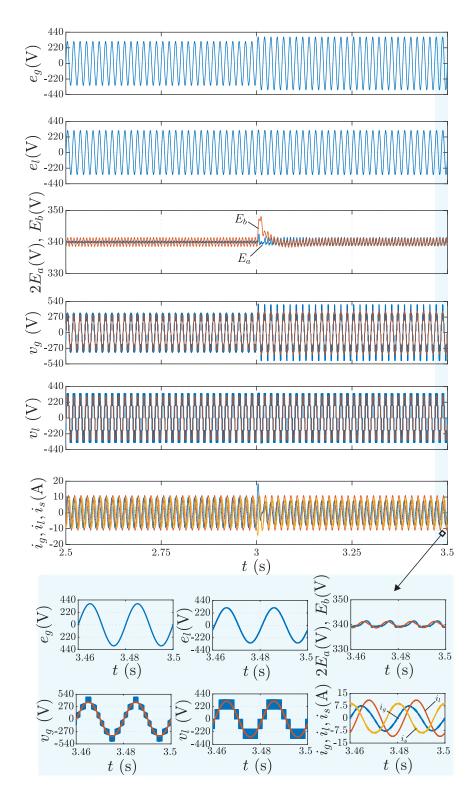

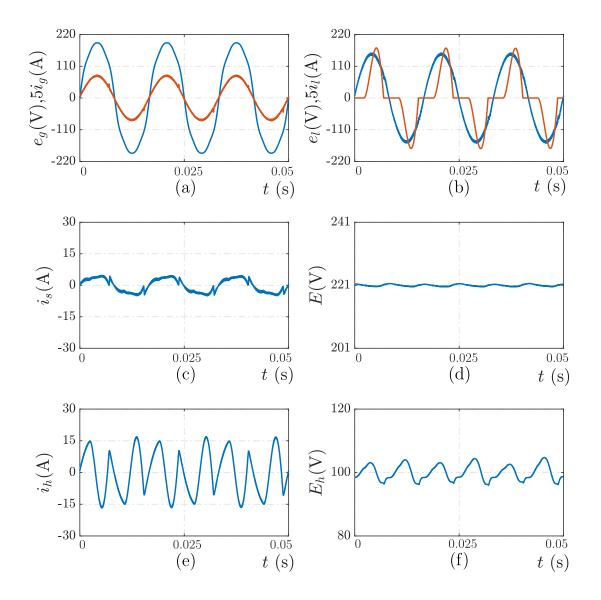

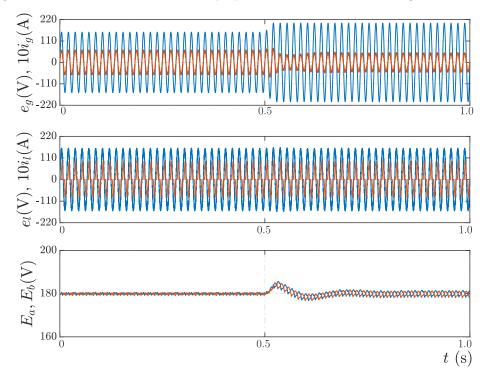

| Figure 2.8  | –Simulation results of the proposed converter in steady state for $\eta =$                        |    |

|             | 2. (a) Grid voltage with $10\%$ of third harmonic, $5\%$ of fifth harmonic,                       |    |

|             | and $2\%$ of seventh harmonic. (b) Load current and shun compensation                             |    |

|             | current. (c) Voltage $(v_{pT})$ and current $(i_{pT})$ in the primary side of the                 |    |

|             | transformer. (d) Voltage $(v_{sT})$ and current $(i_{sT})$ in the secondary side                  |    |

|             | of the transformer. (e) Dc-link voltages $E_a$ . (f) Dc-link voltages $E_b$ . (g)                 |    |

|             | Shunt converter voltage. (h) Series converter voltage                                             | 41 |

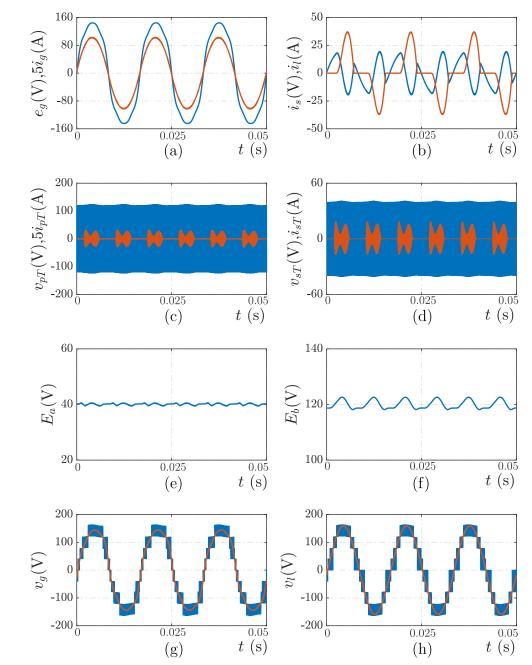

| Figure 2.9  | -Simulation results of the proposed converter in steady state for $\eta =$                  |    |

|-------------|---------------------------------------------------------------------------------------------|----|

|             | 2. (a) Grid voltage with $10\%$ of third harmonic, $5\%$ of fifth harmonic,                 |    |

|             | and $2\%$ of seventh harmonic. (b) Load current and shun compensation                       |    |

|             | current. (c) Voltage $(v_{pT})$ and current $(i_{pT})$ in the primary side of the           |    |

|             | transformer. (d) Voltage $(v_{sT})$ and current $(i_{sT})$ in the secondary side            |    |

|             | of the transformer. (e) Dc-link voltages $E_a$ . (f) Dc-link voltages $E_b$ . (g)           |    |

|             | Shunt converter voltage. (h) Series converter voltage                                       | 42 |

| Figure 2.10 | -Simulation results of the proposed converter under a voltage sag of $20\%$                 |    |

|             | for $\eta = 2$                                                                              | 43 |

| Figure 2.11 | -Simulation results of the proposed converter during a trasient caused                      |    |

|             | by a load power increase of 45% for $\eta = 2. \ldots \ldots \ldots \ldots$                 | 43 |

| Figure 2.12 | -Simulation results of the proposed converter under a voltage sag of $20\%$                 |    |

|             | for $\eta = 3$                                                                              | 44 |

| Figure 2.13 | Simulation results of the proposed converter during a trasient caused                       |    |

|             | by a load power increase of 45% for $\eta = 3. \ldots \ldots \ldots \ldots$                 | 44 |

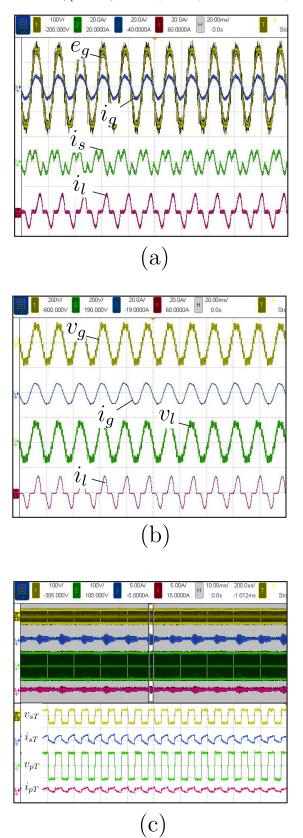

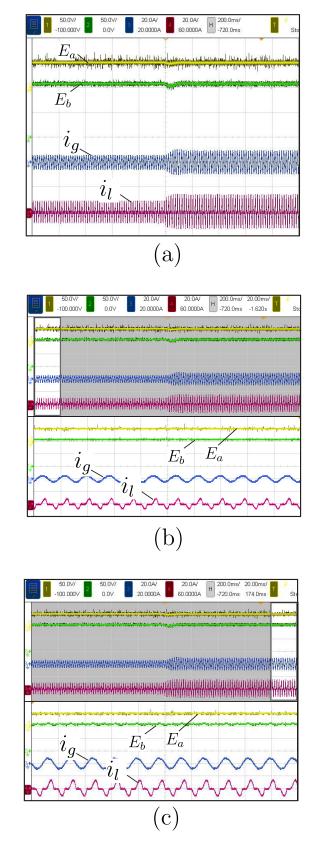

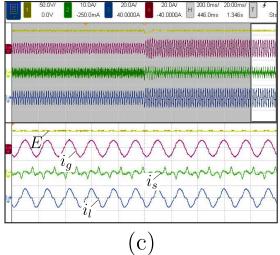

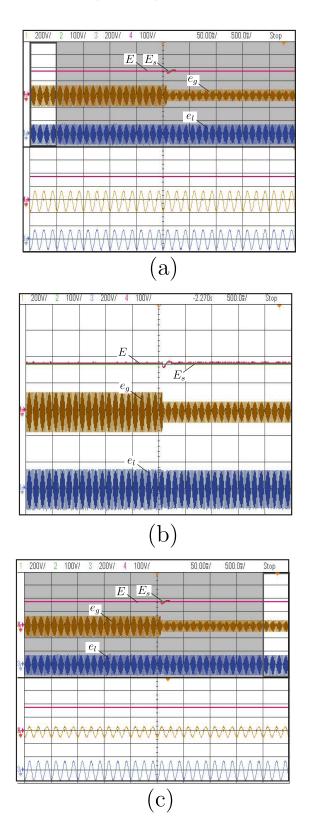

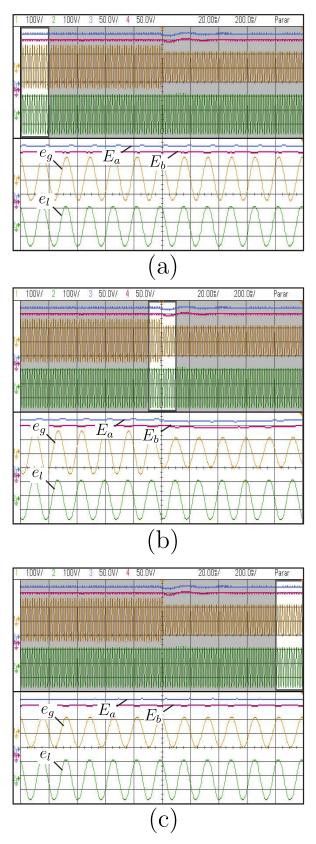

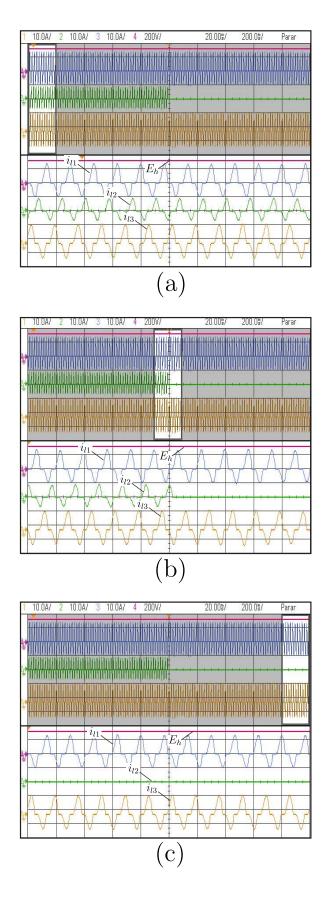

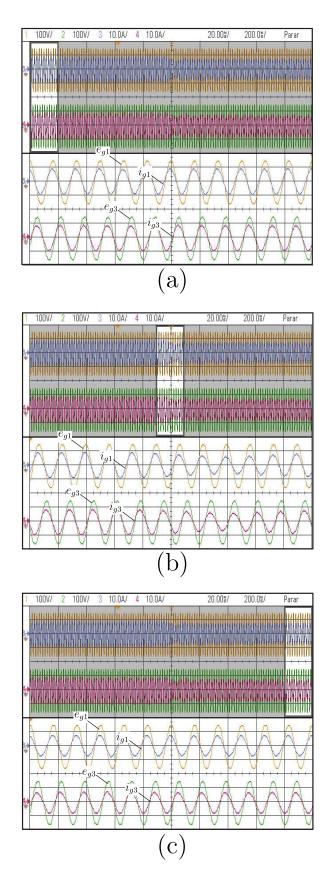

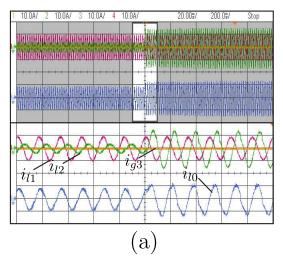

| Figure 2.14 | -Experimental results in steady state for $\eta = 2$ . (a) Grid voltage $(e_g)$ ,           |    |

|             | grid current $(i_g)$ , shunt compensation current $(i_s)$ , and load current $(i_l)$ .      |    |

|             | (b) Shunt and series converter voltage $(v_g \text{ and } v_l)$ . (c) Voltages $(v_{pT},$   |    |

|             | $v_{sT}$ ) and currents $(i_{pT}, i_{sT})$ in the primary and secondary side of the         |    |

|             | transformer.                                                                                | 46 |

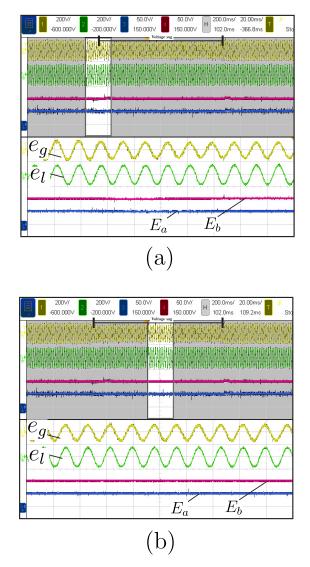

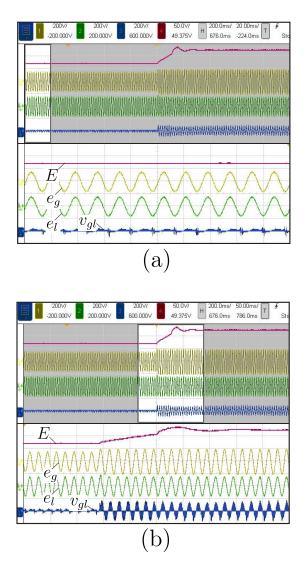

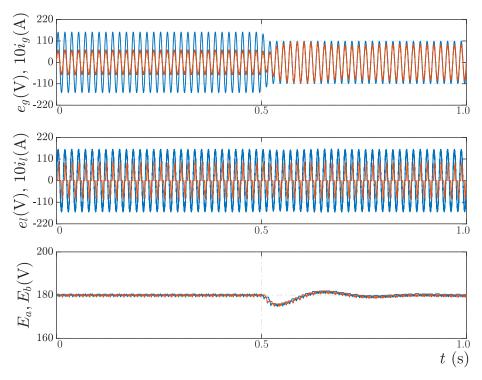

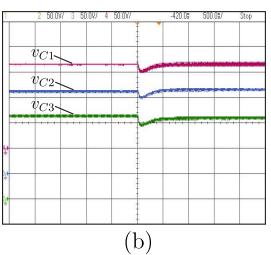

| Figure 2.15 | -Experimental results with a linear load under $20\%$ of grid voltage sag                   |    |

|             | for $\eta = 2$ . (a) Dc-link voltages $(E_a \text{ and } E_b)$ and Grid $(e_g)$ and load    |    |

|             | $(e_l)$ voltages with zoomed view in the beginning of the disturbance. (b)                  |    |

|             | Dc-link voltages $(E_a \text{ and } E_b)$ and Grid $(e_g)$ and load $(e_l)$ voltages with   |    |

|             | zoomed view during the disturbance. (c) Dc-link voltages $(E_a \text{ and } E_b)$           |    |

|             | and Grid $(e_g)$ and load $(e_l)$ voltages with zoomed view in the end of the               |    |

|             | disturbance.                                                                                | 47 |

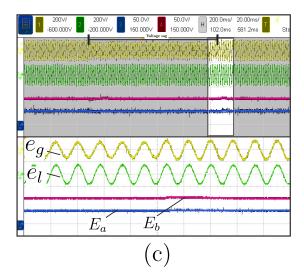

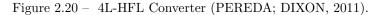

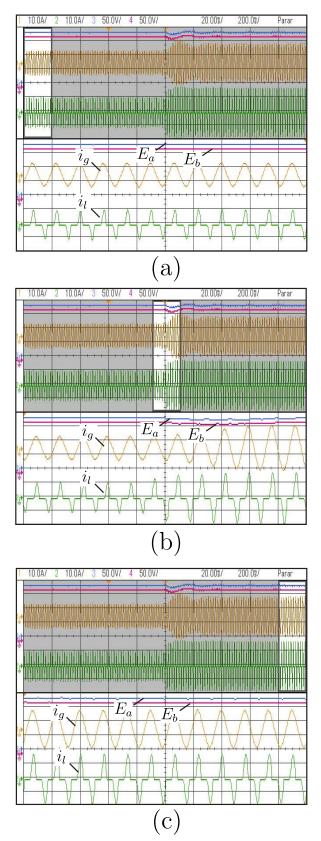

| Figure 2.16 | -Experimental results with a nonlinear load for $\eta = 2$ . (a) Dc-link voltages           |    |

|             | $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load $(i_l)$ currents. (b) Dc-link voltages   |    |

|             | $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load $(i_l)$ currents with zoomed view before |    |

|             | the disturbance. (c) Dc-link voltages $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load    |    |

|             | $(i_l)$ currents with zoomed view after the disturbance                                     | 48 |

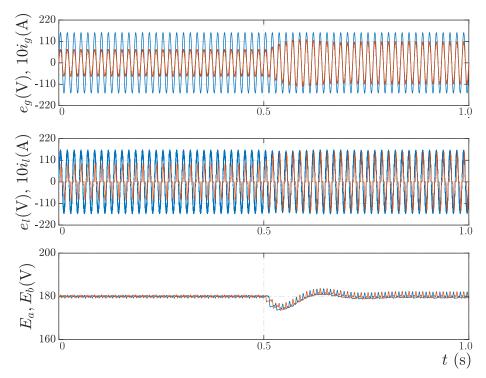

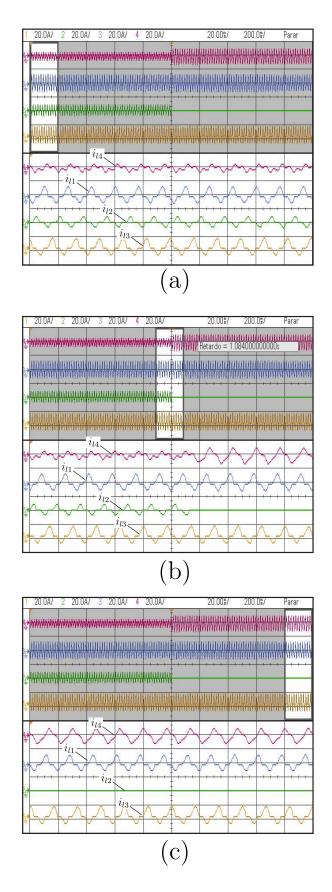

| Figure 2.17 | -Experimental results in steady state for $\eta = 3$ . (a) Grid voltage $(e_g)$ ,           |    |

|             | grid current $(i_g)$ , shunt compensation current $(i_s)$ , and load current $(i_l)$ .      |    |

|             | (b) Shunt and series converter voltage $(v_g \text{ and } v_l)$ . (c) Voltages $(v_{pT},$   |    |

|             | $v_{sT}$ ) and currents $(i_{pT}, i_{sT})$ in the primary and secondary side of the         |    |

|             | transformer                                                                                 | 49 |

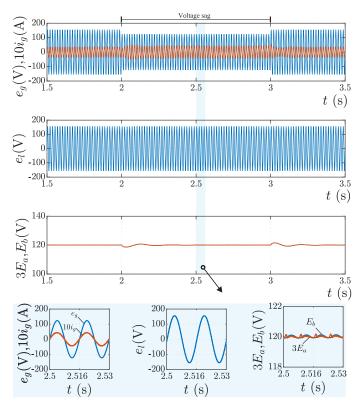

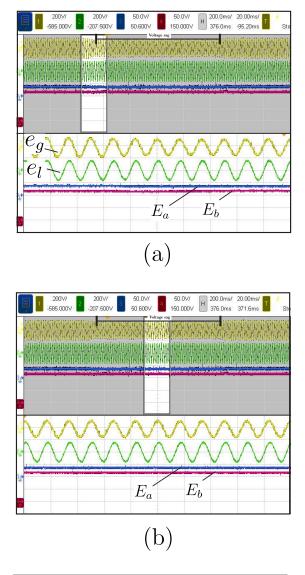

| Figure 2.18 Experimental results with a linear load under 20% of grid voltage sag<br>for $\eta = 3$ . (a) Dc-link voltages $(E_a \text{ and } E_b)$ and Grid $(e_g)$ and load<br>$(e_l)$ voltages with zoomed view in the beginning of the disturbance. (b)<br>Dc-link voltages $(E_a \text{ and } E_b)$ and Grid $(e_g)$ and load $(e_l)$ voltages with<br>zoomed view during the disturbance. (c) Dc-link voltages $(E_a \text{ and } E_b)$<br>and Grid $(e_g)$ and load $(e_l)$ voltages with zoomed view in the end of the<br>disturbance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

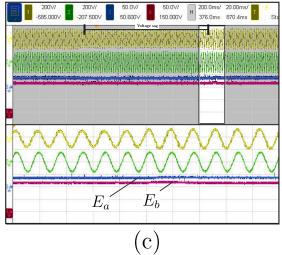

| Figure 2.19 Experimental results with a nonlinear load for $\eta = 3$ . (a) Dc-link voltages $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load $(i_l)$ currents. (b) Dc-link voltages $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load $(i_l)$ currents with zoomed view before the disturbance. (c) Dc-link voltages $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load $(i_l)$ currents with zoomed view before the disturbance. (c) Dc-link voltages $(E_a \text{ and } E_b)$ and grid $(i_g)$ and load $(i_l)$ currents with zoomed view $(E_a \text{ and } E_b)$ and $(i_l)$ currents with zoomed view $(E_a \text{ and } E_b)$ and $(E_b)$ and |   |

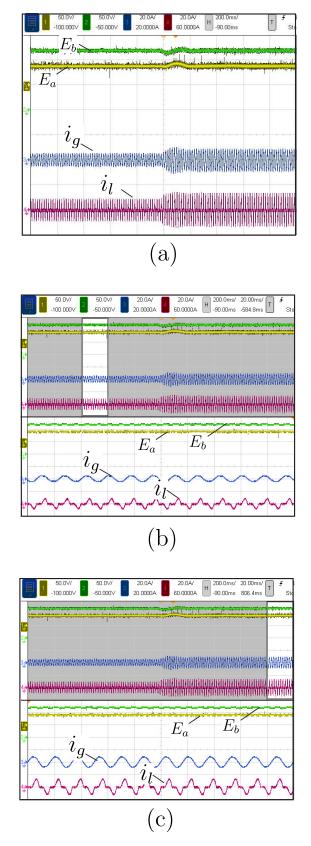

| Figure 2.20 4L-HFL Converter (PEREDA; DIXON, 2011)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 |

| $-E_b = 3E_a \ (\eta = 3). \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 |

| Figure 2.22 Processed power in the HFL for 5L-HFL and 4L-HFL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

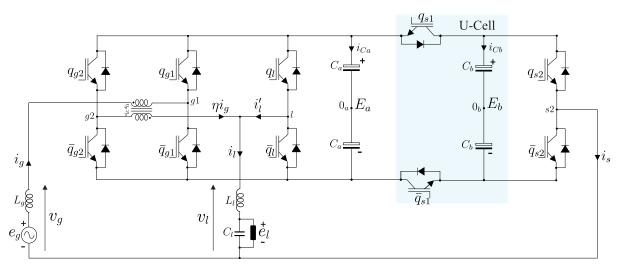

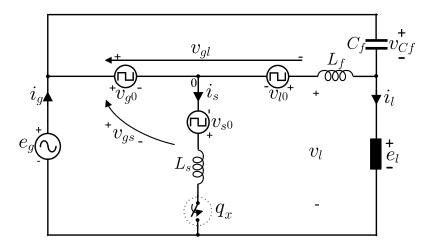

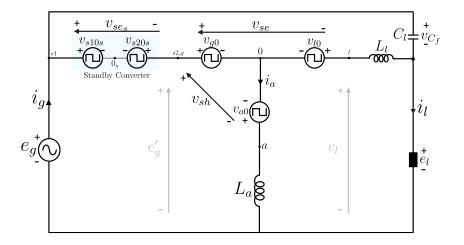

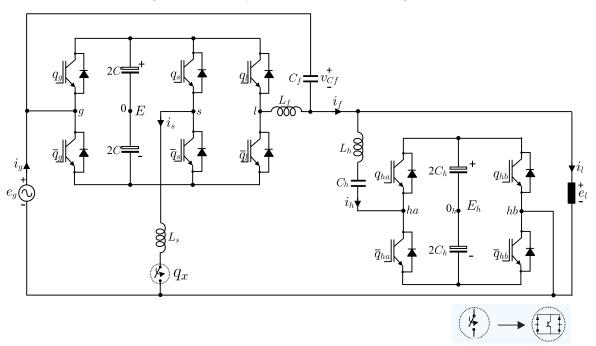

| Figure 3.1 –Proposed ac-dc-ac configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

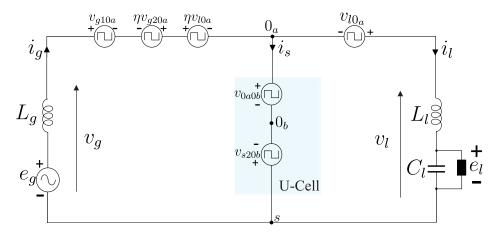

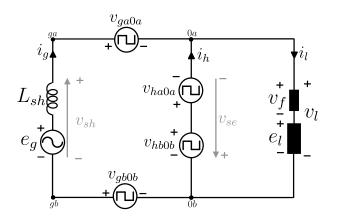

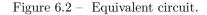

| Figure 3.2 –Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

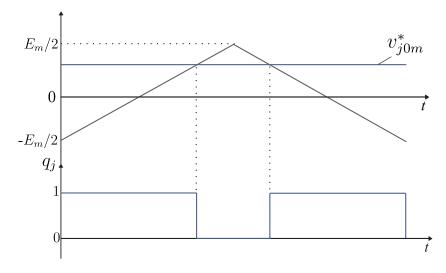

| Figure 3.4 –Carrier-based PWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

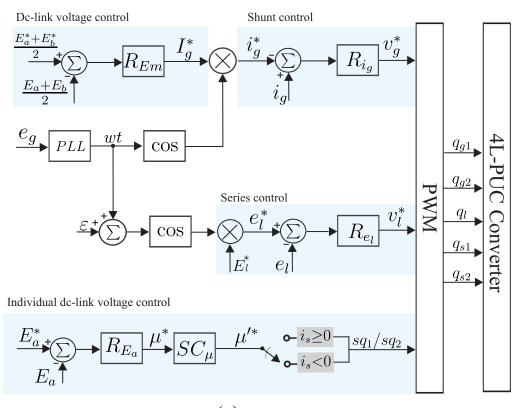

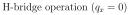

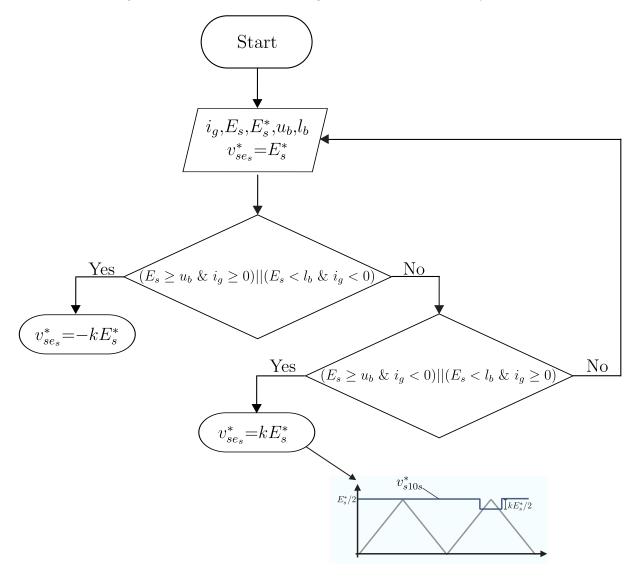

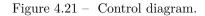

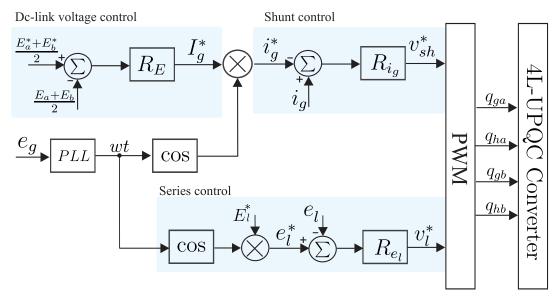

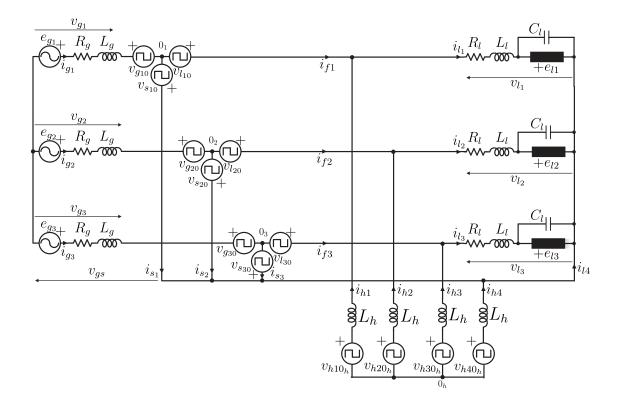

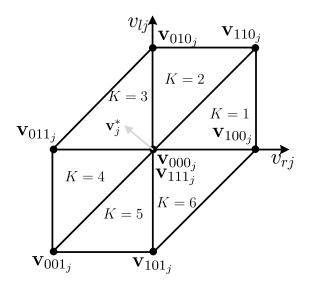

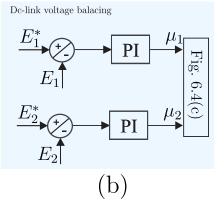

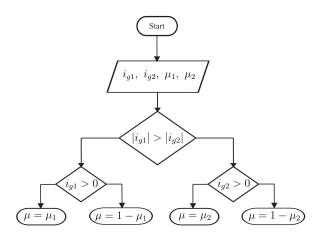

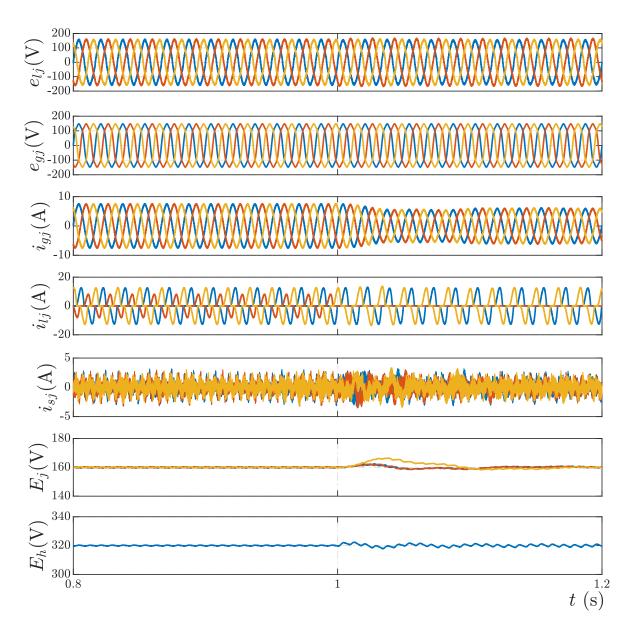

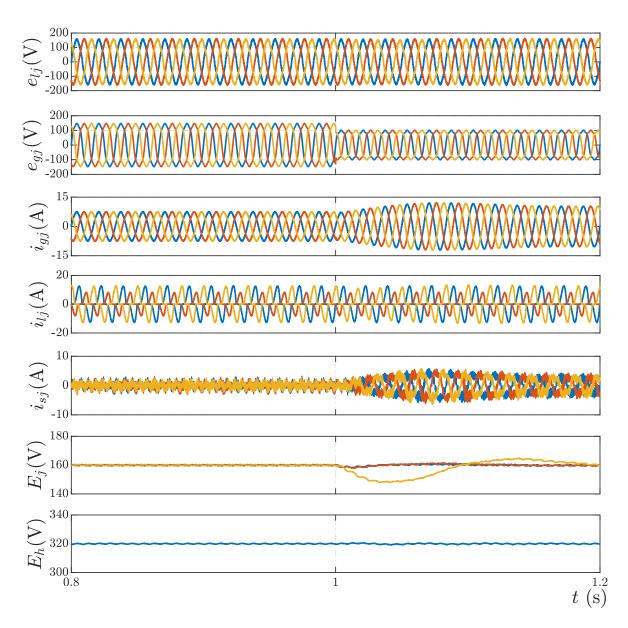

| Figure 3.5 –Overall control system. (a) Control diagram. (b) Flowchart for individual dc-link voltage balancing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9 |

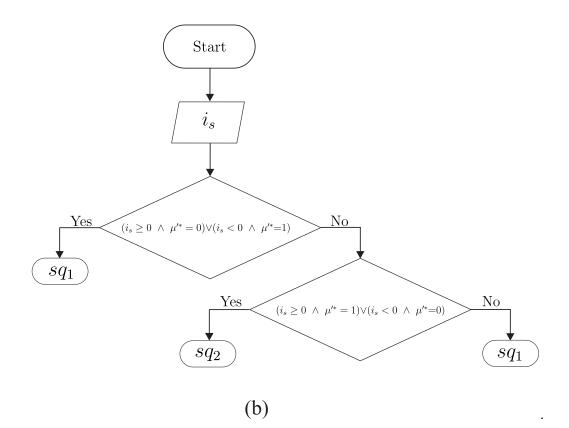

| Figure 3.6 –The power distribution of the dc-link voltage $E_a$ as a function of the amplitude of the grid voltage for $\eta = 1$ . (a) Operation constraints when $E_a$ is selected to charge. (b) Operation constraints when $E_a$ is selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| to discharge. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 |

| Figure 3.7 –Experimental setup used in the tests. 1 - Grid; 2 - Load: nonlinear load<br>+ RL load; 3 - Grid inductance; 4 - Transformer; 5 - Voltage and current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

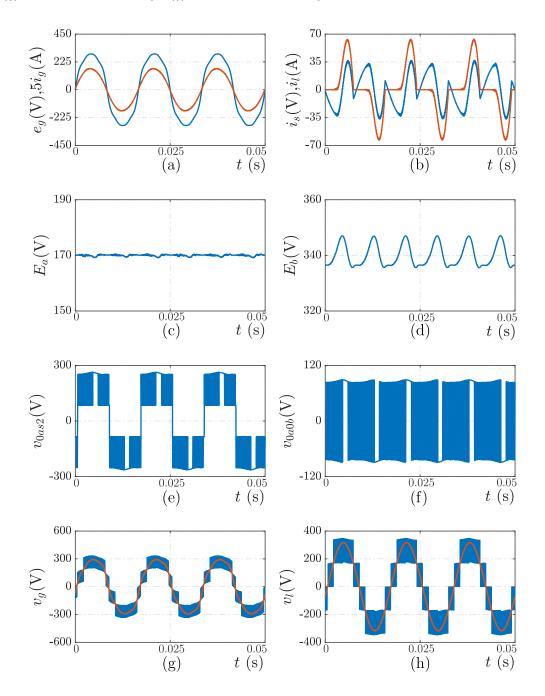

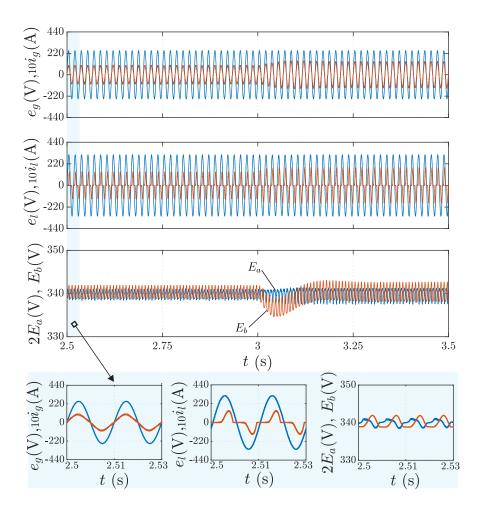

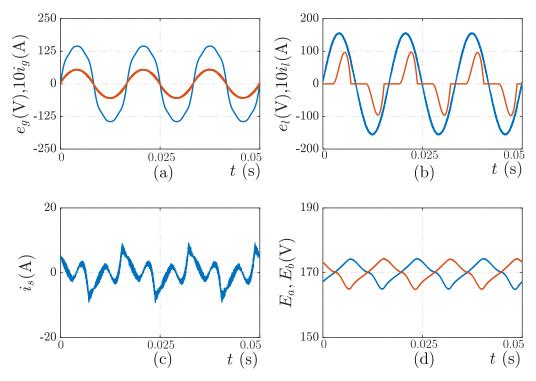

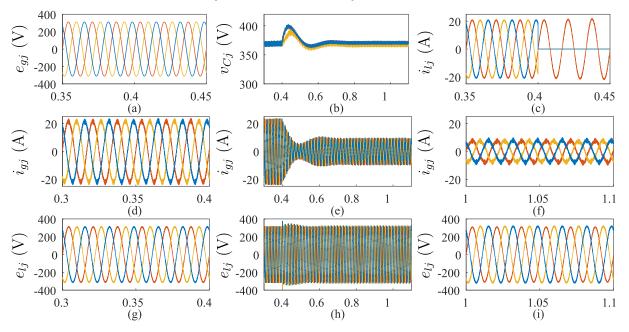

| sensors; 6 - 4L-PUC; 7 - Drivers; 8 - Oscilloscope; 9 - Voltmeters 72<br>Figure 3.8 –Simulation results of the proposed converter operating with grid voltage<br>and load current disturbances under rated conditions. (a) Grid voltage<br>(with 10% of third harmonic, 5% of fifth harmonic, and 2% of seventh<br>harmonic) and grid current. (b) Load current and shunt compensation<br>current. (c) Dc-link voltages $E_a$ . (d) Dc-link voltages $E_b$ . (e) Packed<br>u-cell (PUC) voltage ( $v_0s2$ ). (f) Pole voltage $v_{0a0b}$ .(g) Shunt converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| voltage. (g) Series converter voltage. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 |

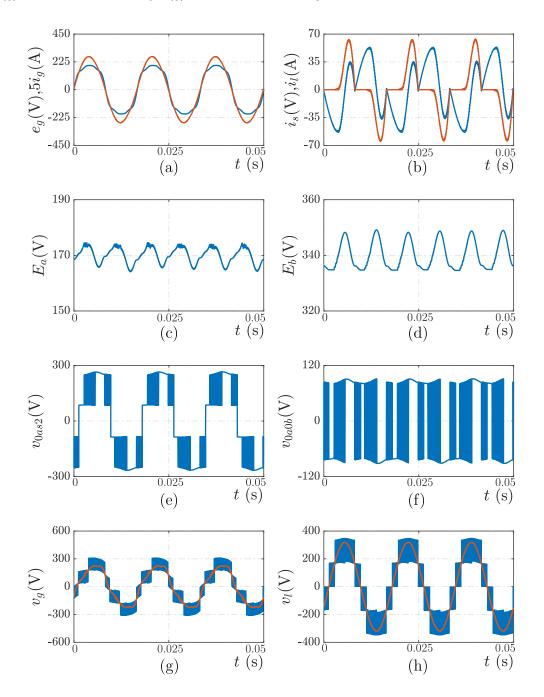

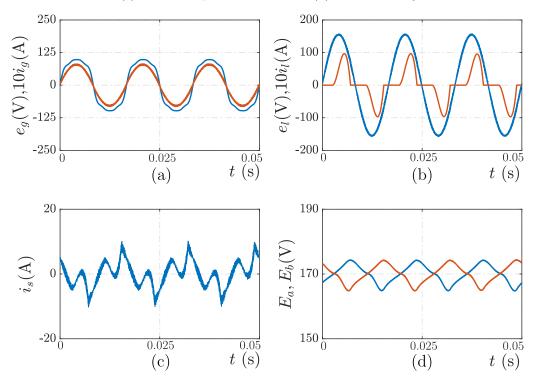

| Figure 3.9  | –Simulation results of the proposed converter operating with grid voltage                  |    |

|-------------|--------------------------------------------------------------------------------------------|----|

|             | and load current disturbances 30% of grid voltage sag. (a) Grid voltage                    |    |

|             | (with $10\%$ of third harmonic, $5\%$ of fifth harmonic, and $2\%$ of seventh              |    |

|             | harmonic) and grid current. (b) Load current and shunt compensation                        |    |

|             | current. (c) Dc-link voltages $E_a$ . (d) Dc-link voltages $E_b$ . (e) Packed              |    |

|             | u-cell (PUC) voltage ( $v_0s2$ ). (f) Pole voltage $v_{0a0b}$ .(g) Shunt converter         |    |

|             | voltage. (g) Series converter voltage                                                      | 74 |

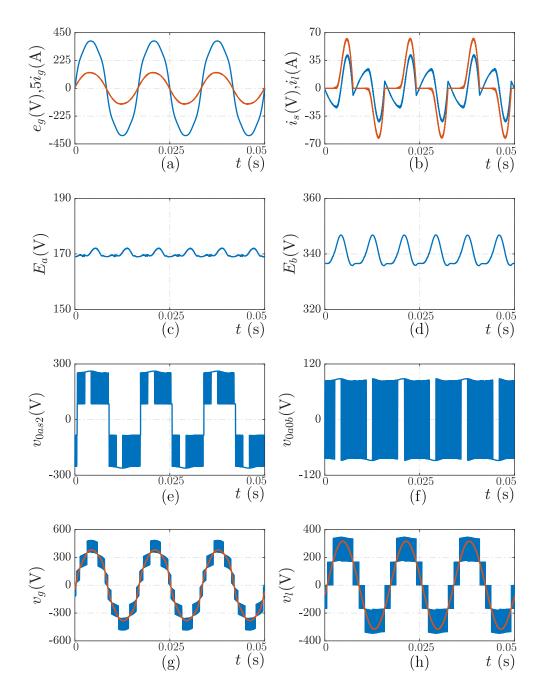

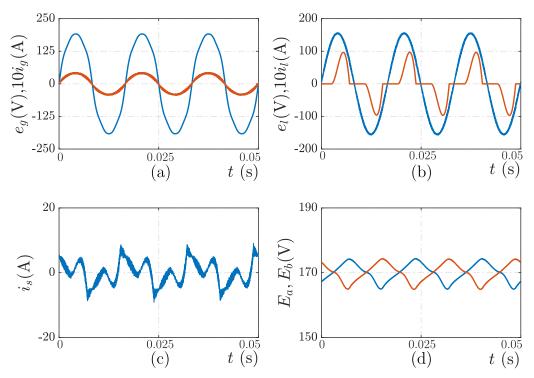

| Figure 3.10 | Simulation results of the proposed converter operating with grid voltage                   |    |

| <u> </u>    | and load current disturbances under 30% of grid voltage swell. (a) Grid                    |    |

|             | voltage (with $10\%$ of third harmonic, $5\%$ of fifth harmonic, and $2\%$                 |    |

|             | of seventh harmonic) and grid current. (b) Load current and shunt                          |    |

|             | compensation current. (c) Dc-link voltages $E_a$ . (d) Dc-link voltages $E_b$ .            |    |

|             | (e) Packed u-cell (PUC) voltage $(v_0s_2)$ . (f) Pole voltage $v_{0a0b}$ .(g) Shunt        |    |

|             | converter voltage. (g) Series converter voltage                                            | 75 |

| Figure 3.11 |                                                                                            | 76 |

|             | Simulation results of the proposed converter under a voltage swell of 20%.                 | 77 |

| Figure 3.13 | Simulation results of the proposed converter under a 20% of voltage sag                    |    |

| -           | and with a step in the load power from $P_l = 1.11$ kW to $P_l = 1.56$ kW.                 | 78 |

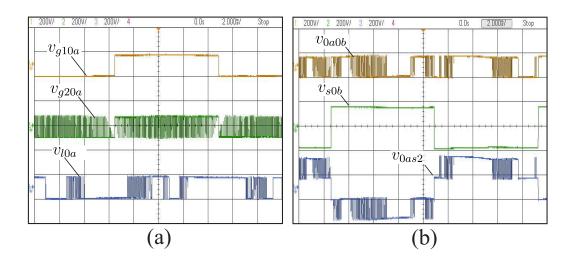

| Figure 3.14 | Experimental results of the pole voltage of each leg, the voltage between                  |    |

| _           | the dc-links midpoints $(v_{0a0b})$ , and the voltage between the dc-link                  |    |

|             |                                                                                            | 79 |

| Figure 3.15 | Experimental results of the pole voltage of each leg, the voltage between                  |    |

|             | the dc-links midpoints $(v_{0a0b})$ , and the voltage between the dc-link                  |    |

|             | midpoint of $C_a$ and leg s2 $(v_{0as2})$ .                                                | 80 |

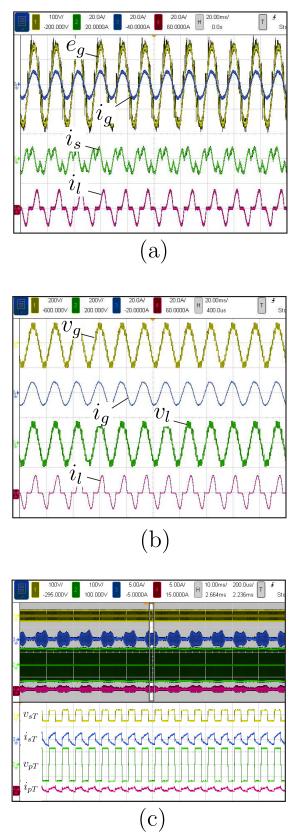

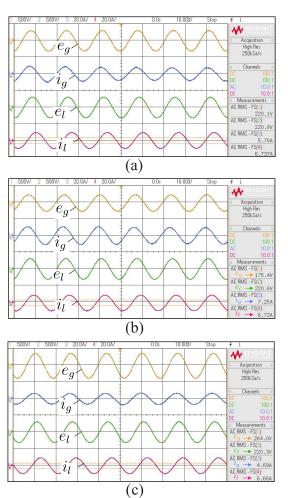

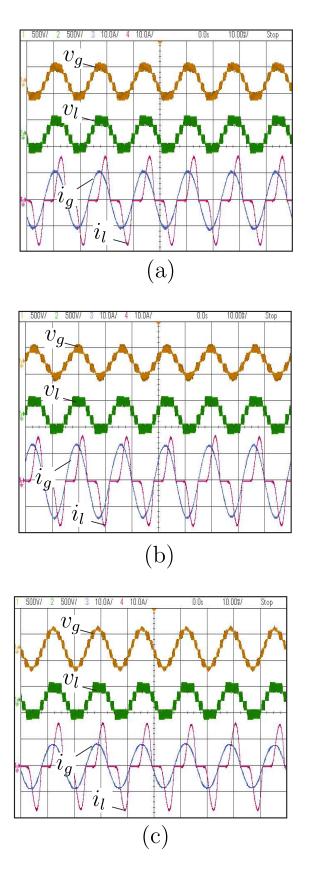

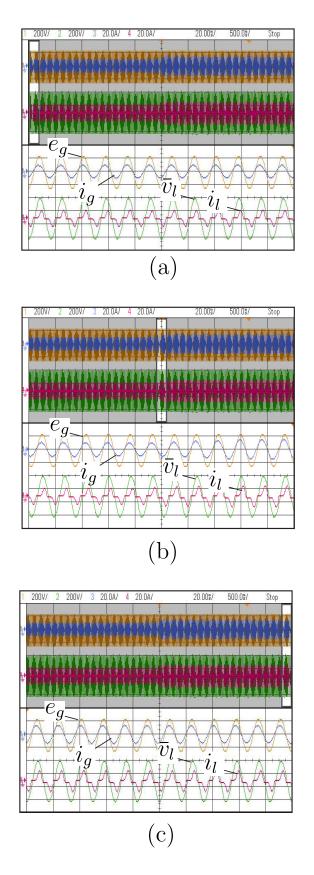

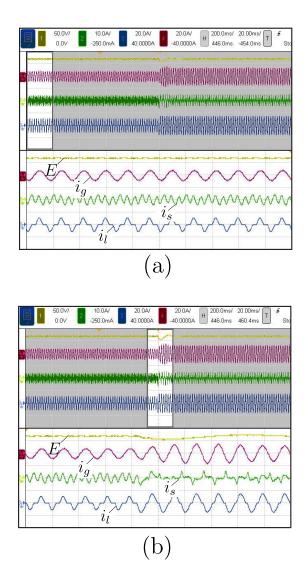

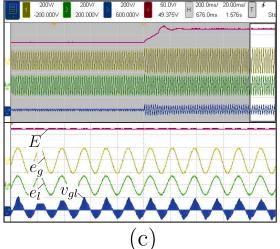

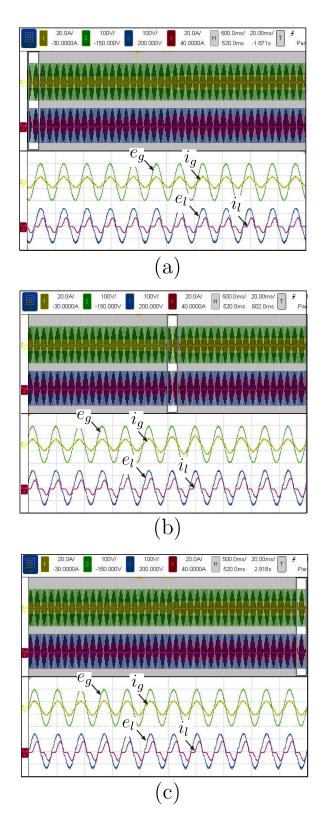

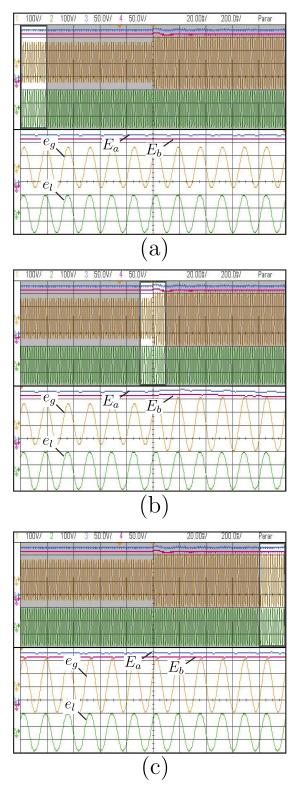

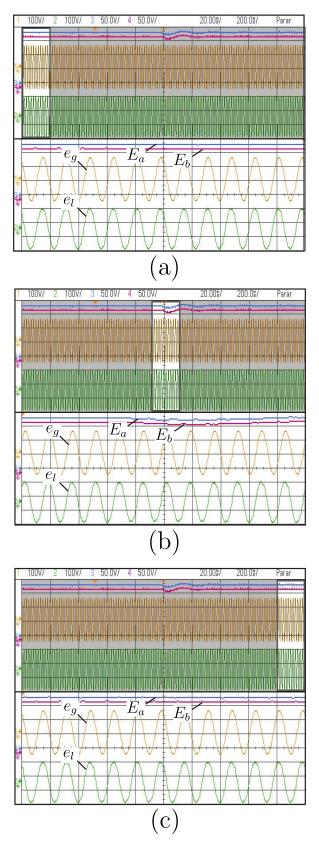

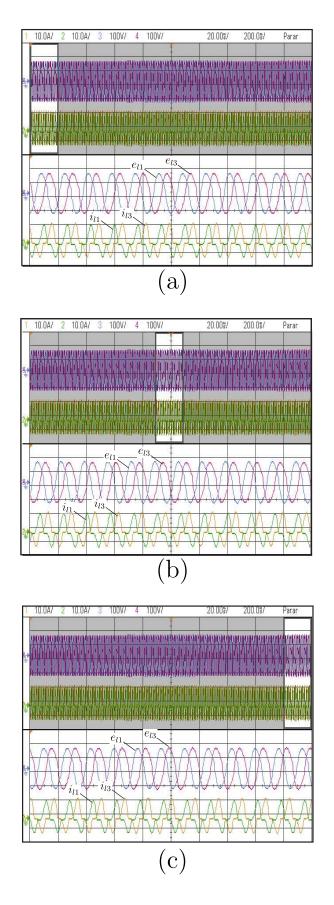

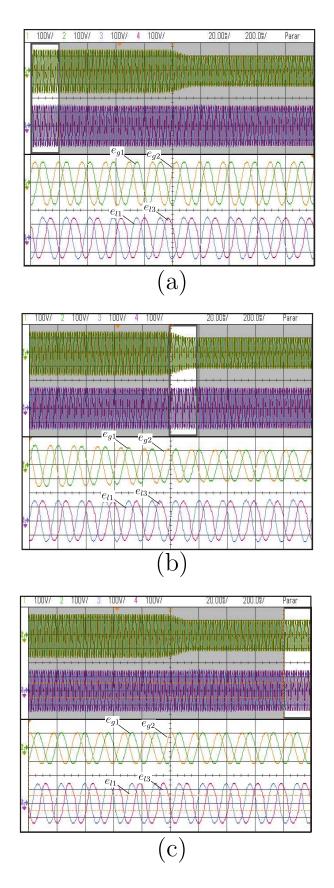

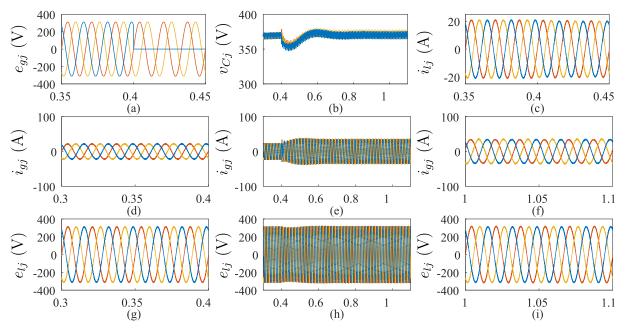

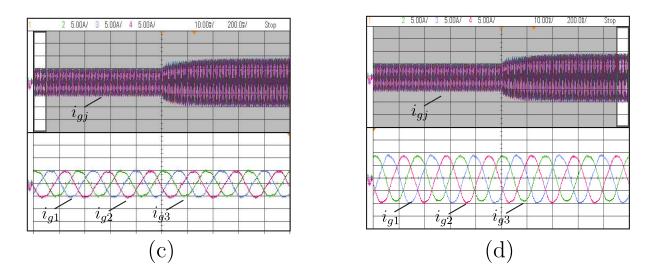

| Figure 3.16 | -Experimental results. Series converter voltage $(v_l)$ , shunt converter                  |    |

|             | voltage $(v_g)$ , grid current $(i_g)$ , and load current $(i_l)$ (a) in rated condition;  |    |

|             | (b) under 20% of voltage sag; (c) uder 20% of voltage swell                                | 81 |

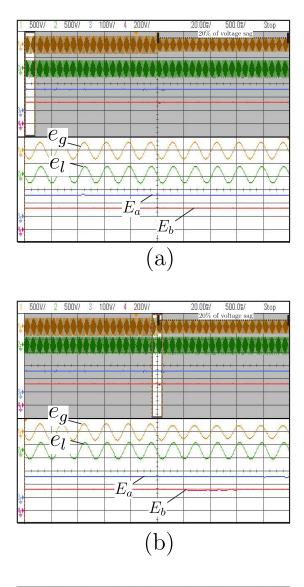

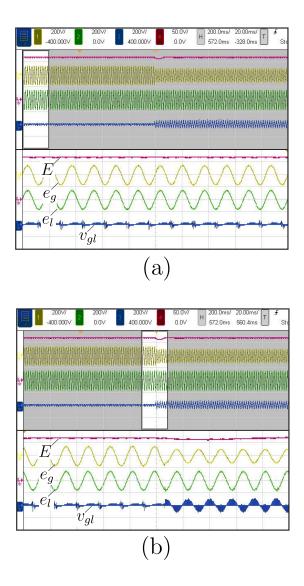

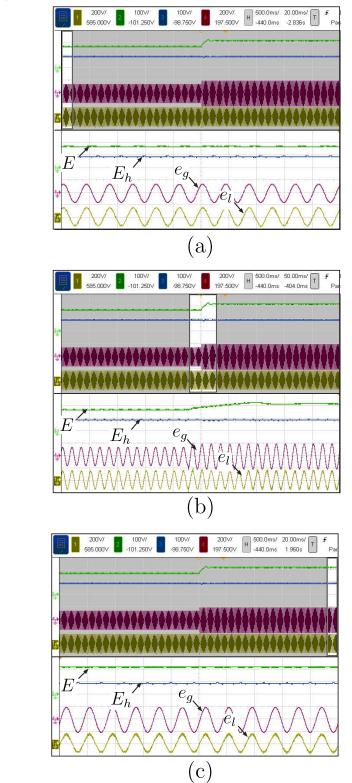

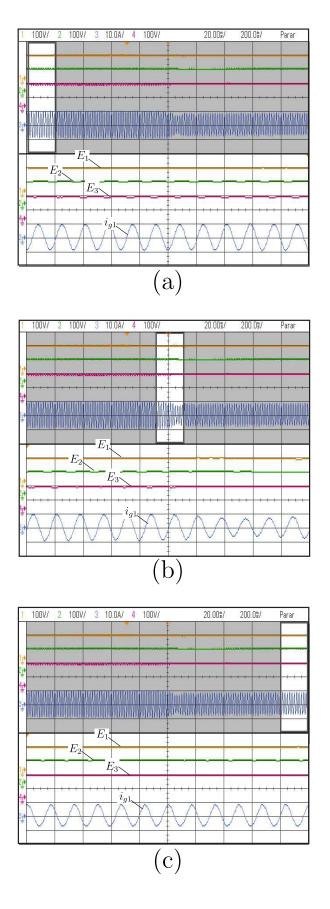

| Figure 3.17 | -Experimental results - Grid voltage sag of 20%. Grid $(e_g)$ and load                     |    |

|             | voltages $(e_l)$ and dc-link voltages $(E_a \text{ and } E_b)$ (a) in rated conditions     |    |

|             | (b) in the beginning of the disturbance, and (c) under 20% of voltage sag.                 | 82 |

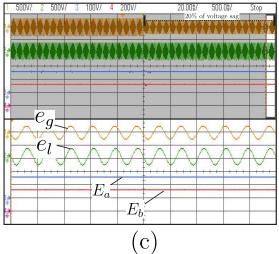

| Figure 3.18 | -Experimental results - Grid voltage swell of 20%. Grid $(e_g)$ and load                   |    |

|             | voltages $(e_l)$ and dc-link voltages $(E_a \text{ and } E_b)$ (a) in rated conditions     |    |

|             | (b) in the beginning of the disturbance, and (c) under $20\%$ of voltage                   |    |

|             | swell                                                                                      | 83 |

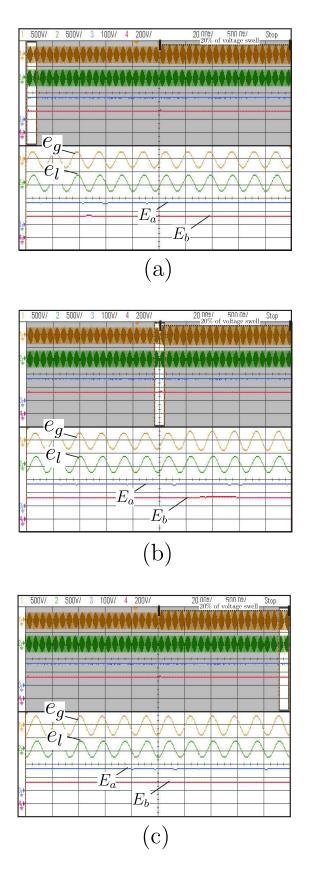

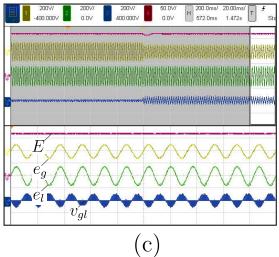

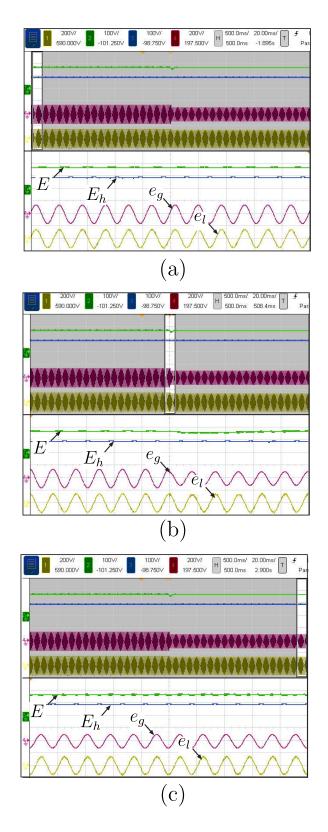

| Figure 3.19 | -Experimental results - Step in the load power from $P_l = 1.11$ kW to                     |    |

|             | $P_l = 1.56$ kW and grid voltage under 20% of voltage sag. (a) Average                     |    |

|             | series converter voltage $(\bar{v}_l)$ , grid voltage $(e_g)$ , grid current $(i_g)$ , and |    |

|             | load current $(i_l)$ (a) before the load transient, (b) in the beginning of                |    |

|             | the load transient, and (c) during the load transient. $\ldots$ $\ldots$ $\ldots$          | 84 |

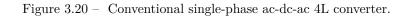

| $Figure \ 3.20$ | -Conventional single-phase ac-dc-ac 4L converter                                                                                                                                                                                                                                                                                    | 85  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

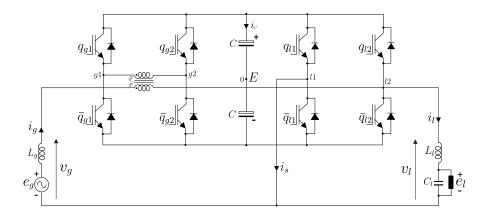

| Figure 3.21     | Power processed by the transformer as a function of the amplitude of                                                                                                                                                                                                                                                                |     |

|                 | the grid voltage.                                                                                                                                                                                                                                                                                                                   | 86  |

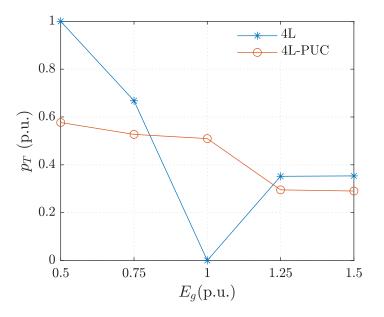

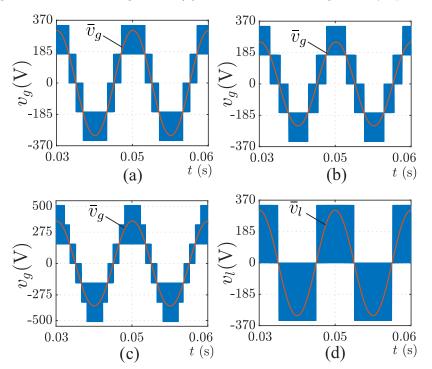

| Figure 3.22     | -Voltages generated by the 4L converter and their average values ( $\bar{v}_g$ and $\bar{v}_l$ ). (a) Shunt converter voltage in rated conditions. (b) Shunt converter voltage under 20% of voltage sag. (c) Shunt converter voltage under 20% of voltage swell. (d) Series converter voltage for any operation scenario.           | 88  |

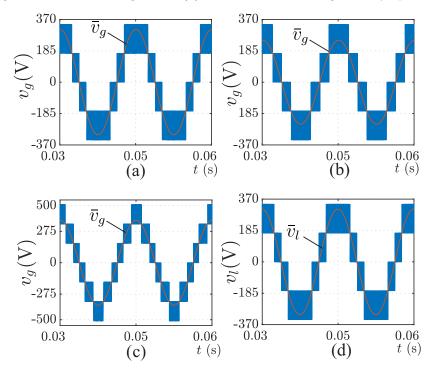

| Figure 3.23     | -Voltages generated by the 4L-PUC converter and their average values $(\bar{v}_g \text{ and } \bar{v}_l)$ . (a) Shunt converter voltage in rated conditions. (b) Shunt converter voltage under 20% of voltage sag. (c) Shunt converter voltage under 20% of voltage swell. (d) Series converter voltage for any operation scenario. | 89  |

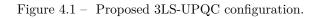

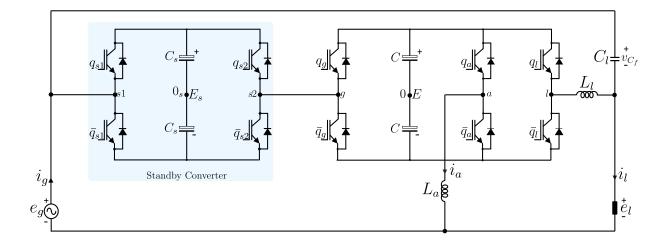

| Figure 4.1      | –Proposed 3LS-UPQC configuration.                                                                                                                                                                                                                                                                                                   | 94  |

|                 |                                                                                                                                                                                                                                                                                                                                     | 95  |

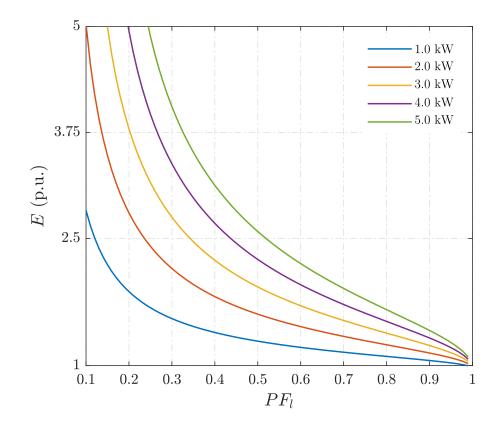

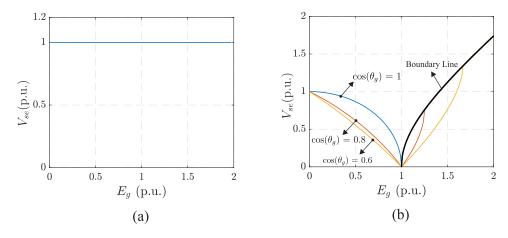

| Figure 4.3      | -Operations constraints of the dc-link voltage (E) of the three-leg con-<br>verters considering a variation in the load power factor and load active                                                                                                                                                                                |     |

|                 | power                                                                                                                                                                                                                                                                                                                               | 97  |

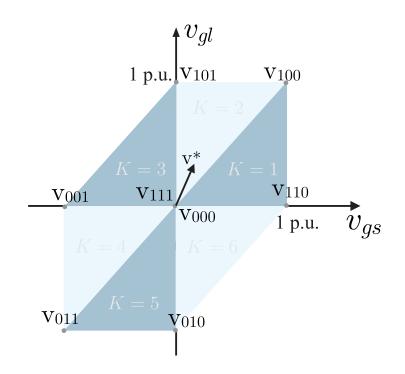

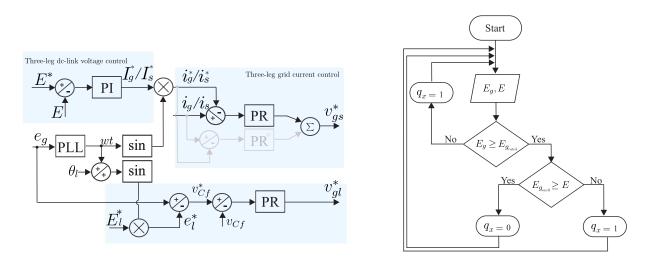

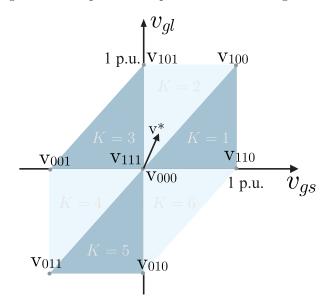

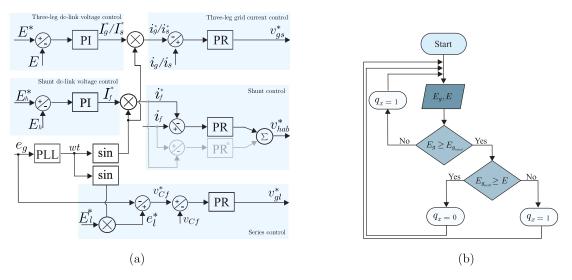

| Figure 4.4      | -Space-vector plane generated by the proposed 3LS-UPQC                                                                                                                                                                                                                                                                              | 99  |

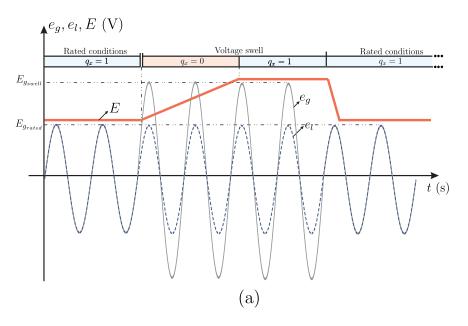

| Figure 4.5      | -Operation under a voltage swell. (a) Idealized representation of a voltage                                                                                                                                                                                                                                                         |     |

|                 | swell transient. (b) Topological state for compensating swells 1                                                                                                                                                                                                                                                                    | .01 |

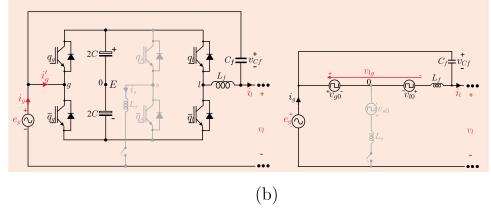

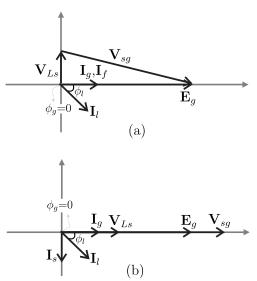

| Figure 4.6      | –Phasor Diagram. (a) Series h-bridge operation. (b) Ac-dc-ac operation                                                                                                                                                                                                                                                              |     |

|                 | during the swell event. (c) Ac-dc-ac operation after the swell event 1                                                                                                                                                                                                                                                              | .02 |

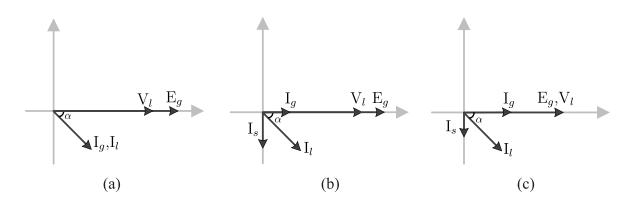

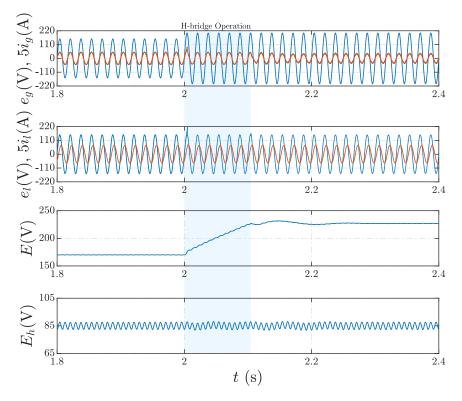

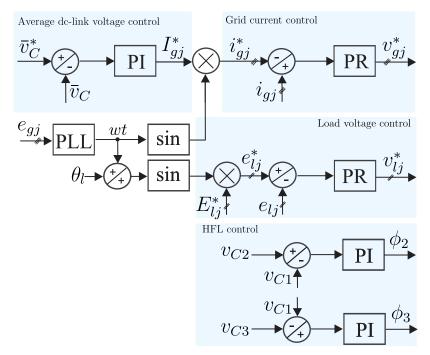

| Figure 4.7      | -Control system. (a) Control diagram to generate the shunt and series                                                                                                                                                                                                                                                               |     |

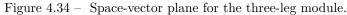

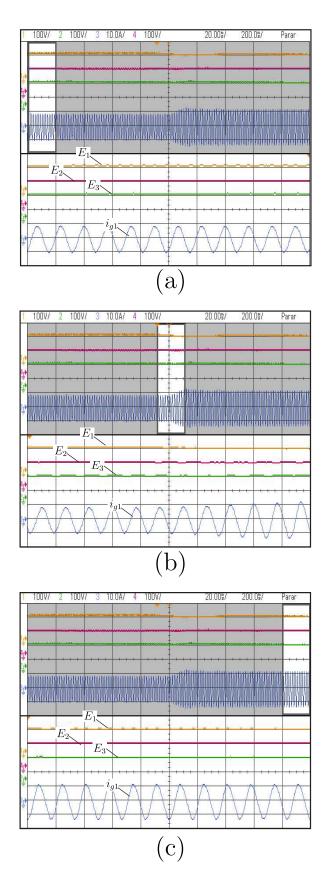

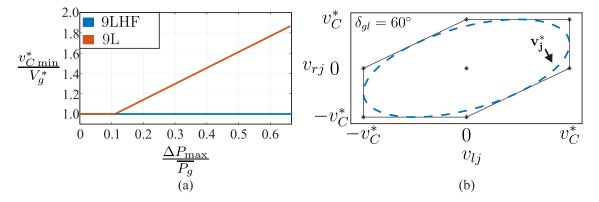

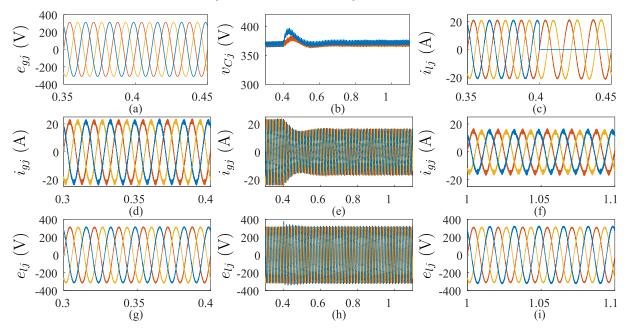

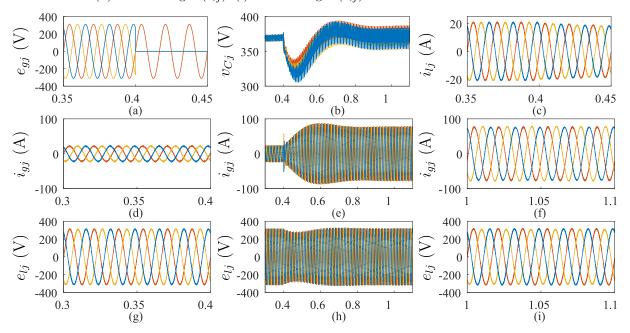

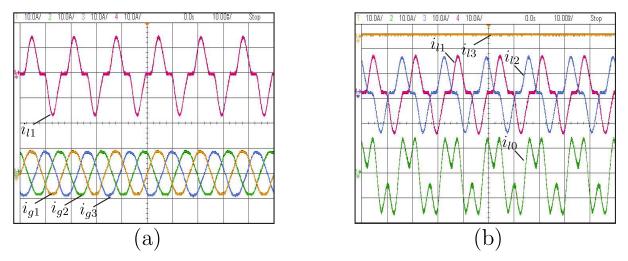

| Figure 4.8      | reference voltages. (b) Flowchat of the $q_x$ operation                                                                                                                                                                                                                                                                             | 102 |

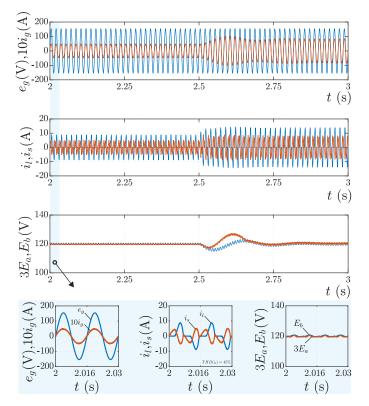

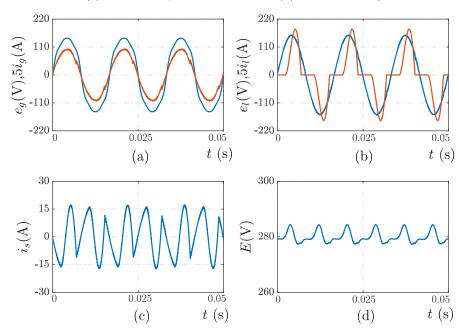

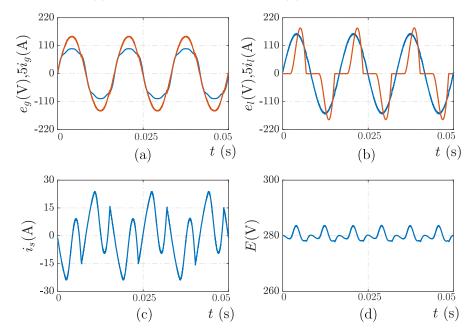

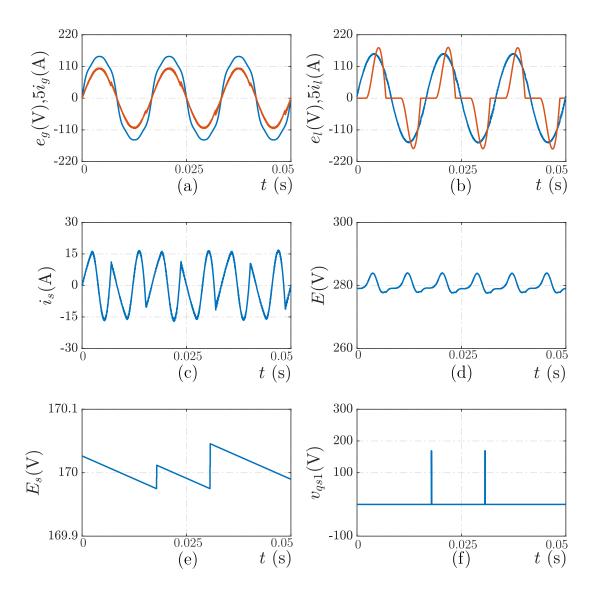

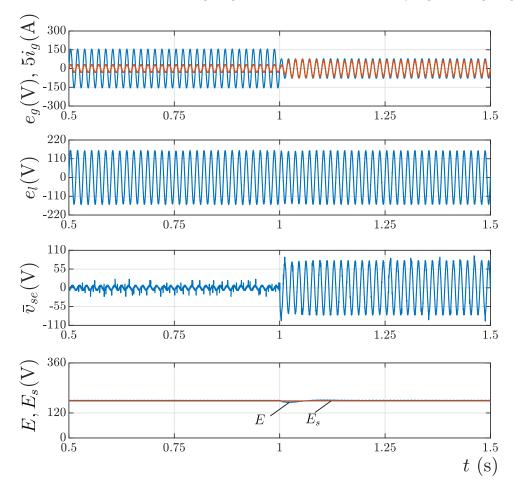

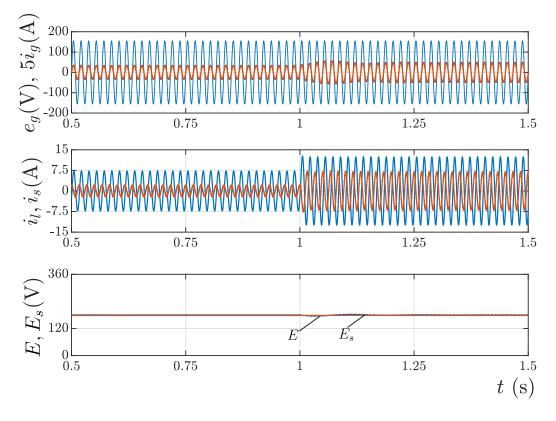

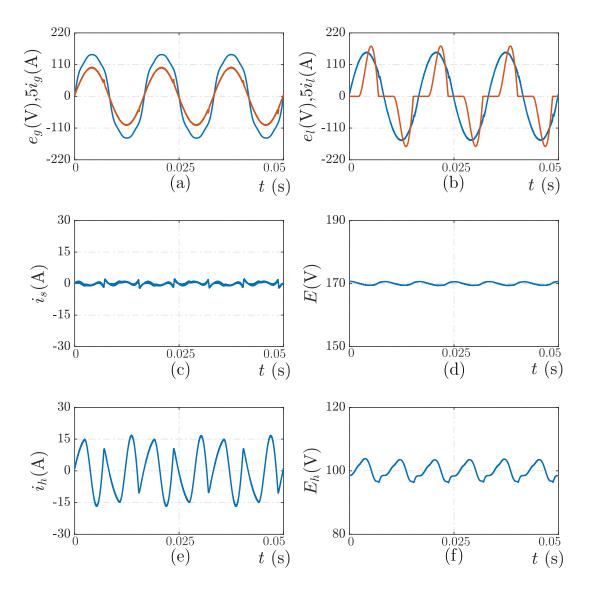

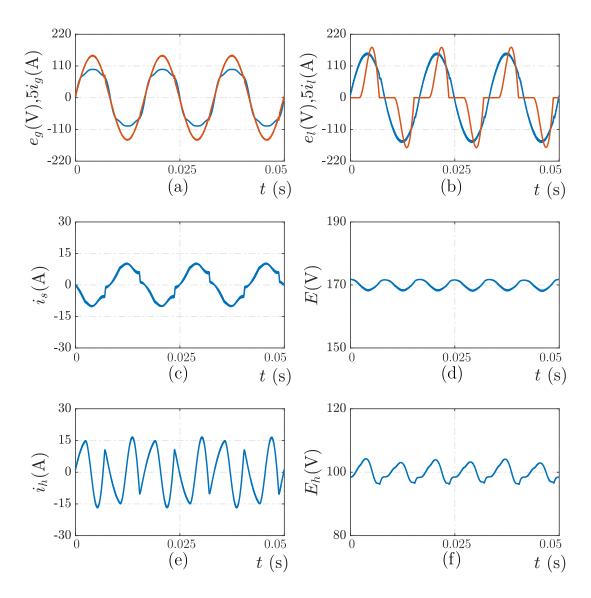

|                 | current. (c) Shunt compensation current. (d) Dc-link voltage $E$ 1                                                                                                                                                                                                                                                                  | .05 |

| Figure 4.9      | -Simulation results of the proposed converter under 30% of grid voltage<br>sag. (a) Grid voltage with 10% of third harmonic, 5% of fifth harmonic,<br>and 2% of seventh harmonic and grid current. (b) Load voltage and                                                                                                             |     |

| D: 4.10         | Load current. (c) Shunt compensation current. (d) Dc-link voltage $E_{\cdot}$ . 1                                                                                                                                                                                                                                                   | 105 |

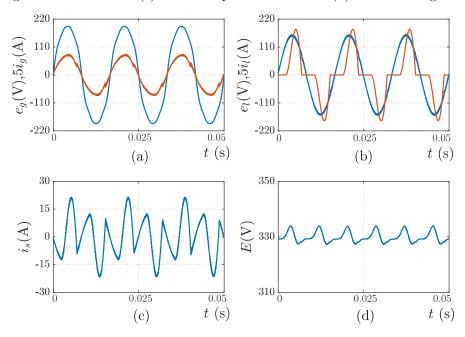

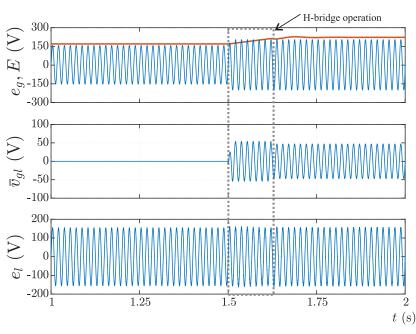

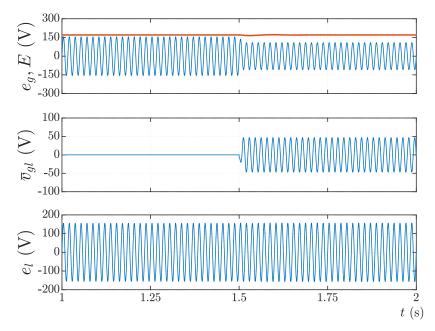

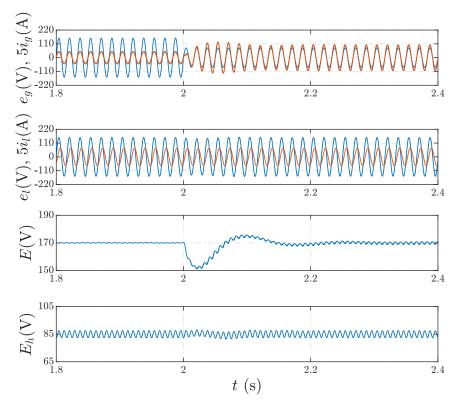

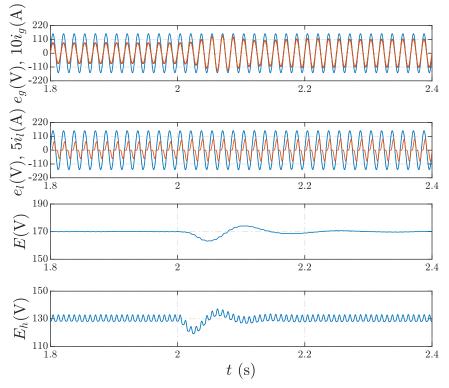

| Figure 4.10     | -Simulation results of the proposed converter under 30% of grid voltage swell. (a) Grid voltage with 10% of third harmonic, 5% of fifth harmonic,                                                                                                                                                                                   |     |

|                 | and 2% of seventh harmonic and grid current. (b) Load voltage and<br>Load current. (c) Shunt componentiation current. (d) De link voltage $F_{1}$                                                                                                                                                                                   | 06  |

| Figuro 4 11     | Load current. (c) Shunt compensation current. (d) Dc-link voltage $E$ . 1<br>-Simulation results with nonlinear load. Transient caused by a load power                                                                                                                                                                              | 100 |

| 1 1guit 4.11    | increased from $P_l = 600$ W to $P_l = 1.1$ kW                                                                                                                                                                                                                                                                                      | .06 |

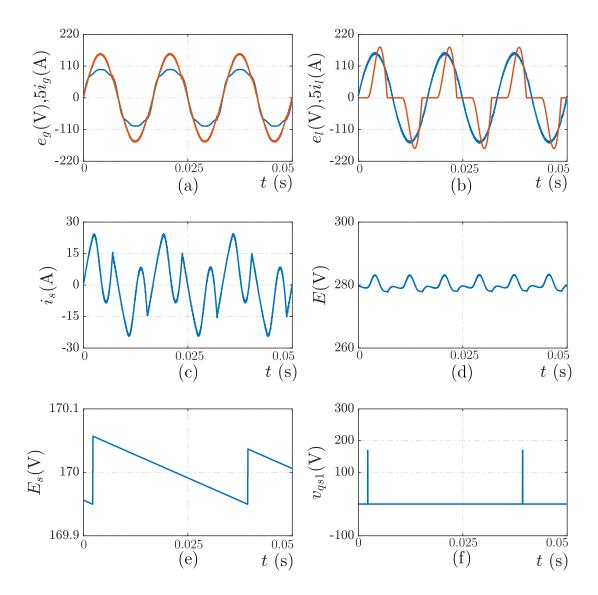

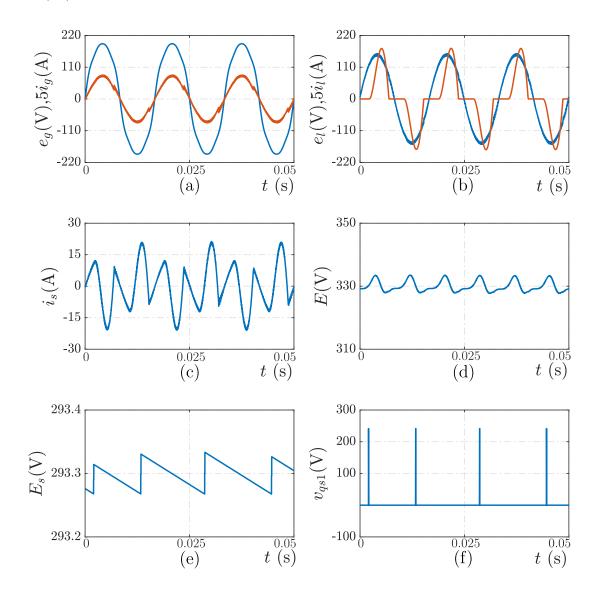

| Figure 4.12  | Simulation results with linear load with load power $P_l = 500$ W under<br>a voltage swell of 30%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.13  | Simulation results with linear load with load power $P_l = 500$ W under<br>a voltage sag of 30%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

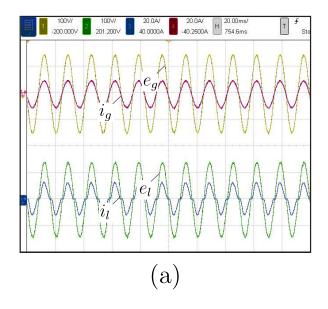

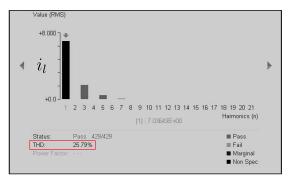

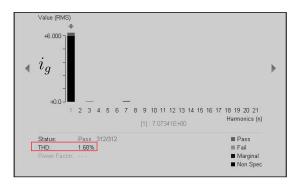

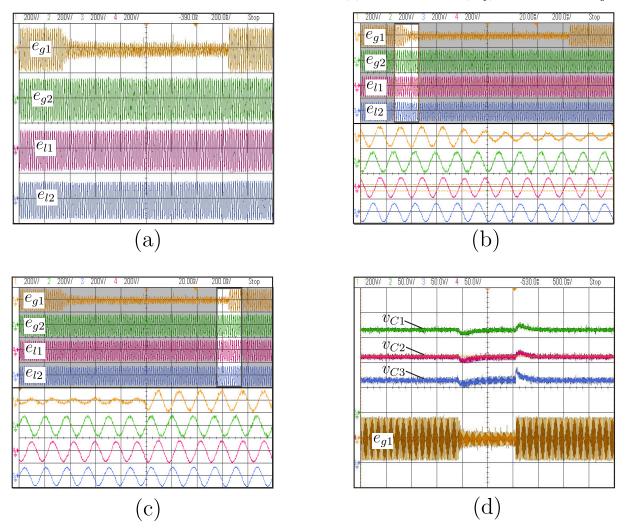

| Figure 4.14  | Experimental results in steady state for THD measurement of the grid<br>and load currents for $v_{gl} = 0$ . (a) Grid voltage $(e_g)$ , grid current $(i_g)$ ,<br>load voltage $(e_l)$ , and load current $(i_l)$ . (b) THD of the load current. (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

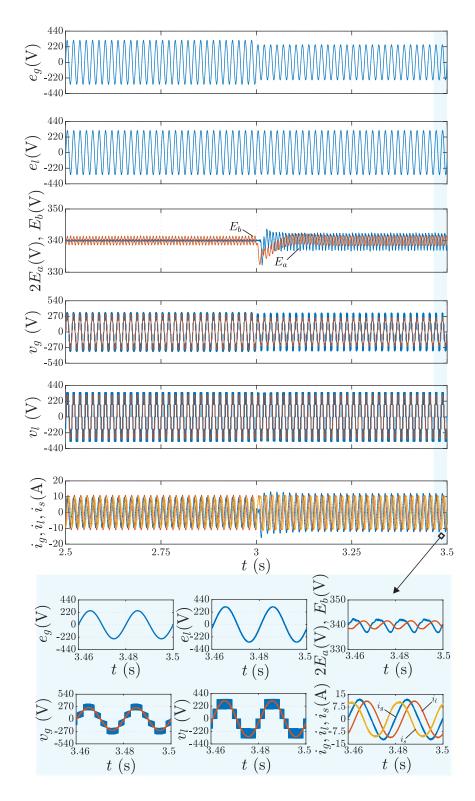

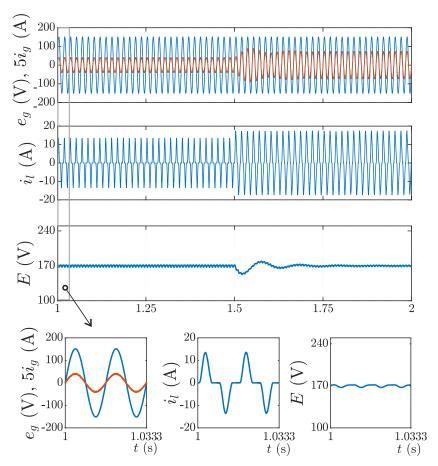

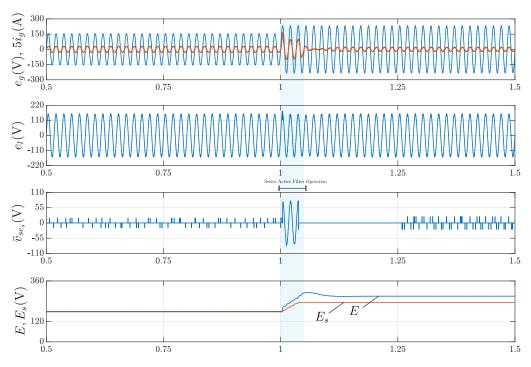

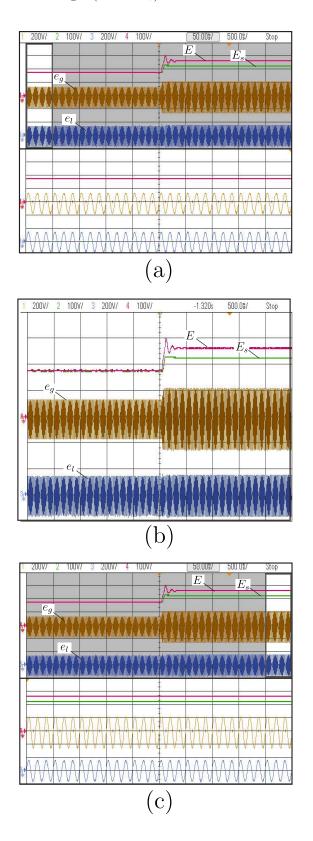

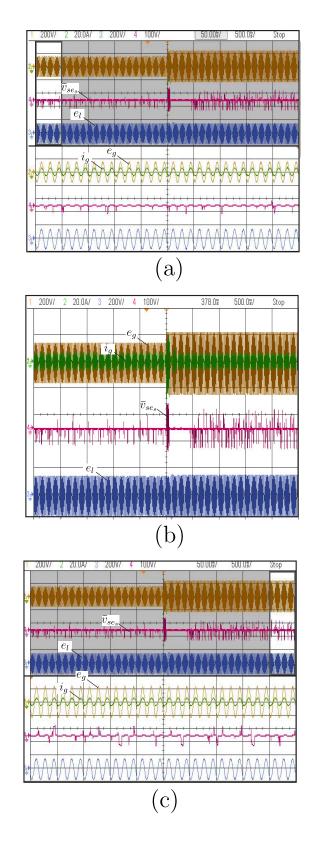

| Figure 4.15  | THD of the grid current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 108 |

| Figure 4.16  | (b) Dc-link voltage $(E)$ , grid current $(i_g)$ , shunt compensation current $(i_s)$ , and load current $(i_l)$ with zoomed view during the load transient (c) Dc-link voltage $(E)$ , grid current $(i_g)$ , shunt compensation current $(i_s)$ , and load current $(i_l)$ with zoomed view after the load transient<br>-Experimental results - Grid voltage swell of 30%. (a) Dc-link voltage                                                                                                                                                                                                                                                                                                          | 109 |