# Análise da Área de Operação Segura e Estudo da Robustez do Transistor MOSFET de Carbeto de Silício

Campina Grande, Brasil

13 de fevereiro de 2017

# Análise da Área de Operação Segura e Estudo da Robustez do Transistor MOSFET de Carbeto de Silício

Trabalho de Conclusão de Curso submetido à Coordenação de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande - Campus de Campina Grande como parte dos requisitos necessários para a obtenção do título de Graduado em Engenharia Elétrica.

Universidade Federal de Campina Grande – UFCG Unidade Acadêmica de Engenharia Elétrica

Orientador: Professor Montiê Alves Vitorino, Dr.

Campina Grande, Brasil 13 de fevereiro de 2017

Análise da Área de Operação Segura e Estudo da Robustez do Transistor MOS-FET de Carbeto de Silício/ João André Soares de Oliveira. – Campina Grande, Brasil, 13 de fevereiro de 2017-

$35~\mathrm{p.}$  ; il. ;  $30~\mathrm{cm.}$

Orientador: Professor Montiê Alves Vitorino, Dr.

Trabalho de Conclusão de Curso – Universidade Federal de Campina Grande –  $\operatorname{UFCG}$

Unidade Acadêmica de Engenharia Elétrica , 13 de fevereiro de 2017.

# Análise da Área de Operação Segura e Estudo da Robustez do Transistor MOSFET de Carbeto de Silício

Trabalho de Conclusão de Curso submetido à Coordenação de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande - Campus de Campina Grande como parte dos requisitos necessários para a obtenção do título de Graduado em Engenharia Elétrica.

| Trabalho apro | ovado em: de o                                      | de 2017 |

|---------------|-----------------------------------------------------|---------|

|               | Professor Montiê Alves Vitorino, Orientador         | Dr.     |

|               | Gutemberg Gonçalves dos Sant<br>Júnior<br>Convidado | os      |

Campina Grande, Brasil 13 de fevereiro de 2017

$Este\ trabalho\ \'e\ dedicado\ a\ Deus,\ aos\ meus\ pais,\\ orientador\ e\ aos\ meus\ amigos.$

## Agradecimentos

Primeiramente agradeço a Deus por todas as coisas boas que Ele tem me proporcionado, pela minha saúde e pelas oportunidades que me surgiram.

Aos meus pais Maria Moania Soares e Demontier Gonçalves de Oliveira, por serem os melhores pais que um filho pode ter. Proporcionaram-me tudo do melhor, educação, saúde, carinho, amor, acompanharam-me em minha trajetória de estudos e em todas as minhas conquistas.

A minha avó (vó Neném, em memória) que durante o começo de minha jornada depositou-me uma confiança inabalável, sempre com palavras de motivação, carinho e amor.

A todos os professores e funcionários do Departamento de Engenharia Elétrica da UFCG, em especial ao meu orientador Montiê Alves Vitorino, que me acompanha há quatro anos em minhas atividades acadêmicas e de pesquisa, estando presente em cada momento de minha caminhada, e ao coordenador do DEE, Damásio Fernandes Júnior, por toda a dedicação no cumprimento exemplar de sua função.

Ressalto também minha felicidade em todos os momentos que pude passar, conversando com os amigos Tchaikovsky Oliveira e Adail Ferreira da Silva Paz. Mais que funcionários do Departamento de Engenharia Elétrica da UFCG, eles foram vitais neste percurso, sempre oferencendo palavras de apoio, motivação e boas risadas.

Ao meu amigo Joel-Louis Koné, pela parceria no Laboratório IPES em Lyon, França, pelas pausas de café, discussões e toda a ajuda dada para concluir este trabalho.

Aos meus amigos de Campina Grande, em especial ao grupo de *whatsapp* JackDaniels, que me acompanharam nesta trajetória árdua, com o máximo de companherismo e apoio, indo desde horas intensivas de estudo, até momentos de descontração e lazer.

Aos meus companheiros fraternos que tive a sorte de encontrar neste caminho: Paulo Vinícius, Paulo Mendel, Guilherme Dantas, João Batista e Gilberto Matos.

### Resumo

Este trabalho foi desenvolvido de forma paralela ao desenvolvimento de um módulo de potência para aplicações aeronáuticas, no laboratório IPES em Lyon, França. O objetivo principal é de avaliar a robustez do óxido metálico dos componentes de potência à grande largura de banda, em particular os semicondutores MOSFET SiC comercializados desde 2011. De fato, os componentes de carbeto de silício apresentam inúmeras vantagens em comparação aos de silício, destacando sua resistência específica mais baixa que reduz as perdas por condução. A utilização dos MOSFET SiC é de forte interesse no campo das aplicações ferroviárias e aeronáuticas. O estudo realizado começa por fazer um estado da arte sobre a área de operação segura dos MOSFETs, delimitada de forma clássica pelo estado passante, o limite de tensão ou comportamento em avalanche, o limite de corrente ou comportamento em curto-circuito e o limite térmico definido pela potência máxima. Um melhoramento da área segura é proposto, em sequência, bem como uma nova área de operação segura é definida por um limite de potência-tempo. Por fim, a previsão dos limites para proteger o componente permite abordar a robustez do óxido metálico da porta dos MOSFETs.

Palavras-chave: Área de Operação Segura, MOSFET, Carbeto de Silício, Aplicações Aeronáuticas.

### **Abstract**

This work was developed at the same time as the developemment of a power module for aircrafts applications in Laboratory IPES in Lyon, France. The main object is to evaluate the robustness of the gate oxide of the semiconductors wide-gap components, particularly SIC MOSFET marketed since 2011. Indeed the silicon Carbide present many advantages compared to silicon including a lower specific resistance reducing conduction losses. The use of SiC MOSFET has become very interesting in rail or aviation applications. This study start by making a state of the art on the MOSFET safety area defined conventionally by the on-state limit, the breakdown voltage limit or avalanche phenomenon, the current or short circuit limit and thermal limit defined by the maximum power. An improvement in the safety area is proposed later and a new safety area defined by a boundary time-power. Finally prediction of the limits to protect our component allows us to address the robustness of the gate oxide.

Key-words: Safety Operating Area, MOSFET, Silicon Carbide, Aircrafts Applications.

# Lista de ilustrações

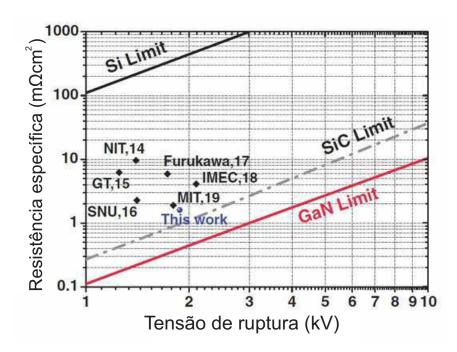

| Figura 1 – Resistência específica em função do comportamento de tensão             | 3  |

|------------------------------------------------------------------------------------|----|

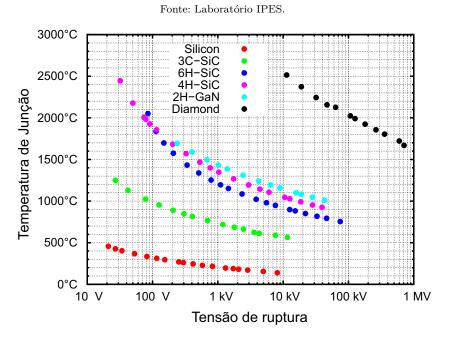

| Figura 2 — Temperatura máxima de junção em função da tensão de ruptura             | 3  |

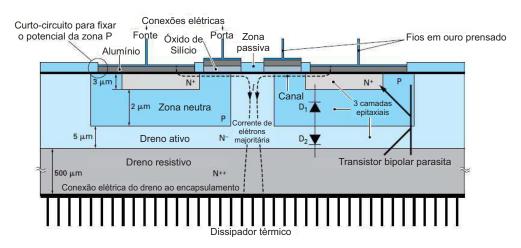

| Figura 3 – Esquema de camadas eletricamente dopadas em detalhe dos MOSFETs.        | 4  |

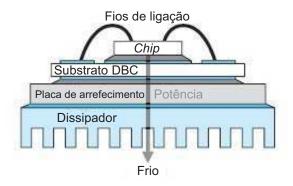

| Figura 4 – Fluxo térmico em um módulo de potência                                  | 6  |

| Figura 5 — Princípio de funcionamento do MOSFET do tipo N                          | 8  |

| Figura 6 – Característica de saída do MOSFET                                       | 9  |

| Figura 7 – Típica curva SOA para um MOSFET de potência                             | 10 |

| Figura 8 – Influciência da corrente de dreno em função da temperatura de junção    |    |

| e do regime pulsado                                                                | 12 |

| Figura 9 – Área de operação segura para um MOSFET de potência                      | 13 |

| Figura 10 – Área de operação segura reversa para um MOSFET de potência             | 13 |

| Figura 11 – Diagrama para a resistência térmica de um dispositivo com dissipador   |    |

| de calor                                                                           | 15 |

| Figura 12 – Transiente de resposta térmica do sistema                              | 16 |

| Figura 13 – Impedância térmica em função do tempo de quebra do MOSFET              | 17 |

| Figura 14 – Modelagem térmica do sistema em estado estático                        | 17 |

| Figura 15 – Modelagem térmica do sistema em estado dinâmico                        | 18 |

| Figura 16 – Determinação da resistência térmica para um dissipador a aletas        | 19 |

| Figura 17 – Área de Operação Segura com resfriamento ao ar livre                   | 21 |

| Figura 18 – Relação entre a resistência de passagem normalizada e a temperatura    |    |

| de junção                                                                          | 22 |

| Figura 19 – Corrente nominal em função da temperatura de junção                    | 23 |

| Figura 20 – Área de Operação Segura do componente com um dissipador a aletas       | 24 |

| Figura 21 – Área de Operação Segura do componente com uma placa de água            | 24 |

| Figura 22 – Superposição das Áreas de Operação Segura para o resfriamento ao ar    |    |

| livre, a aletas e utilizando um dissipador com placa de água                       | 25 |

| Figura 23 – Aproximação não-linear para a SOA do MOSFET de SiC                     | 26 |

| Figura 24 – Área de operação segura em potência-tempo para diferentes ensaios      | 28 |

| Figura 25 – Exemplo de ensaio em curto-circuito $V_{DS}=600V,T_{amb}=25^{\circ}C.$ | 29 |

| Figura 26 – Previsão do tempo de vida útil para o MOSFET SiC                       | 29 |

# Lista de tabelas

| Tabela 1 – 1 | Limites máximos de utilização                    | 5 |

|--------------|--------------------------------------------------|---|

| Tabela 2 – G | Características elétricas do MOSFET estudado     | 5 |

| Tabela 3 – 0 | Características térmicas do MOSFET estudado.     | 6 |

| Tabela 4 – 7 | Analogia entre as grandezas térmicas e elétricas | 5 |

# Lista de abreviaturas e siglas

IPES Integrated Power Electronics Systems.

UMR Unité Mixte de Recherche.

DC Direct Current (Corrente Contínua).

MOSFET Metal Oxide Semiconductor Field Effect Transistor.

SiC Carbeto de Silício.

SOA Safe Operating Area (Área de Operação Segura).

EMC Electromagnetic Compatibility (Compatibilidade Eletromagnética).

FBSOA Forward Biased Safe Operating Area.

RBSOA Reverse Biased Safe Operating Area.

TDDB Time Dependent Dielectric Breakdown

### Lista de símbolos

$I_{DS(DC)}$  Corrente de dreno (contínua).

$I_{DS(pulse)}$  Corrente de dreno (em regime pulsado).

$V_{GS}$  Tensão porta-fonte.

$P_{total}$  Potência total dissipada.

$T_i$  Temperatura de junção.

$T_a$  Temperatura ambiente.

$V_{(BR)DSS}$  Tensão de ruptura.

$V_{th}$  Tensão limiar.

$R_{DS(on)}$  Resistência específica (resistência à estado passante).

$R_{\theta JC}$  Resistência térmica junção-caixa.

$R_{\theta CS}$  Resistência térmica caixa-dissipador.

$R_{\theta SA}$  Resistência térmica dissipador-ambiente.

$Z_{\theta JA}$  Impedância térmica junção-ambiente

$Z_{\theta JC}$  Impedância térmica junção-caixa.

$T_p$  Tempo de ruptura.

# Sumário

| 1                                 | INTRODUÇÃO 1                                                                                     |

|-----------------------------------|--------------------------------------------------------------------------------------------------|

| 2<br>2.1<br>2.2                   | APRESENTAÇÃO                                                                                     |

| <ul><li>2.3</li><li>2.4</li></ul> | Folha de Dados do MOSFET CREE C2M0080120D (1200V, 80 m $\Omega$ ) 5 Utilização de Dissipadores 6 |

| 3                                 | FUNDAMENTAÇÃO TEÓRICA8                                                                           |

| 3.1                               | Estado da Arte sobre a Área de Operação Segura dos MOSFETs 8                                     |

| 3.1.1                             | Estudo da Característica de Saída do MOSFET                                                      |

| 3.1.2                             | Área de Operação Segura                                                                          |

| 3.2                               | Resfriamento do MOSFET SiC                                                                       |

| 3.3                               | Modo de Funcionamento do MOSFET                                                                  |

| 3.3.1                             | Determinação da Impedância Térmica Junção-encapsulamento 16                                      |

| 3.3.2                             | Modelagem Térmica                                                                                |

| 3.4                               | Influência do Tipo de Dissipador Térmico                                                         |

| 4                                 | PLOTAGEM DA ÁREA DE OPERAÇÃO SEGURA DO MOSFET                                                    |

|                                   | SIC CREE                                                                                         |

| 4.1                               | Método Utilizado para o Traçado da SOA                                                           |

| 4.2                               | Comparação das SOAs em Função do Tipo de Resfriamento 24                                         |

| 4.3                               | Aproximação Não-linear para Plotagem da Área de Operação Segura 25                               |

| 5                                 | ANÁLISE DA ROBUSTEZ DO MOSFET 27                                                                 |

| 5.1                               | Novos Conceitos                                                                                  |

| 5.2                               | Robustez do Transistor MOSFET                                                                    |

| 5.3                               | Previsão da vida útil do MOSFET SiC em função de $V_{GS}$ 29                                     |

| 6                                 | CONCLUSÃO 31                                                                                     |

|                                   | REFERÊNCIAS 32                                                                                   |

|                                   | APÊNDICES 34                                                                                     |

|                                   | APÊNDICE A – RESISTÊNCIA TÉRMICA JUNÇÃO-ENCAPSULAMENTO                                           |

|                                   | E ENCAPSULAMENTO-AMBIENTE 35                                                                     |

# 1 Introdução

O carbeto de silício é utilizado desde os anos 1800, porém a aplicação em semicondutores é dita recente. Suas vantagens vão desde uma banda de energia maior, possibilitanto suportar tensões substancialmente maiores, em comparação aos componentes de silício, até valores para resistência específica nitidamente inferiores. Tudo isso, além de outras características, ocasiona menores perdas por comutação e condução, além da possibilidade de operação em altas frequências (maiores que 20 MHz). Do ponto de vista térmico, a condutividade do carbeto de silício é cerca de três vezes maior que dos componentes somente de silício, assim, eles possuem um melhor sistema de arrefecimento natural. [1]

Neste projeto será estudo a área de operação segura para os MOSFETs de SiC comercializados pela empresa CREE. A tensão de operação será de 1200 V, tendo em vista que o escopo deste trabalho fez parte de uma pesquisa paralela ao desenvolvimento de um inversor para aplicações aeronáuticas sob alimentação constante. [1] [2]

De forma clássica, a área de segurança para operação é delimitada pelos limites de tensão ou seu comportamento em avalanche, pelo limite de corrente ou seu comportamento em curto-circuito e pelo limite térmico, definido pela potência máxima dissipada. Um circuito teste para simulação da área de operação será proposto, bem como uma metodologia de estimação de parâmetros. Além disso, um estudo dedicado à robustez do MOSFET de SiC foi realizado, de forma breve, com apresentação de alguns resultados experimentais gerados a partir de uma máquina de testes HVS (*High Voltage Step*) para avalanche, disponibilizada pelo laboratório Ampère. [3]

Este trabalho se apresenta em cinco partes: a primeira consiste da apresentação do contexto de estudo, a segunda remete-se aos estudos bibliográficos, a terceira parte diz respeito ao caso prático considerando sistemas de arrefecimento distintos e a quarta parte trata-se da robustez do MOSFET de carbeto de silício (SiC). [4] [5] [6]

# 2 Apresentação

#### 2.1 Contexto de Estudo

O Laboratório IPES concentra suas missões sobre a elaboração de sistemas elétricos e eletrônicos de potência para o desenvolvimento de um avião com mais eletrônica embarcada. Em efeito, com a multiplicação dos acionadores elétricos a bordo dos aparelhos e a supressão dos sistemas hidráulicos e pneumáticos, gera-se uma grande demanda de sistemas eletrônicos que respondam ao trabalho em condições severas: fortes variações de temperatura (-50 °C à 220 °C), componentes de comutação rápida e normas EMC.

O carbeto de silício é utilisado desde muito tempo (anos 1800), mas para aplicações em semicondutores seu uso é recente [7]. Em relação aos componentes de silício, os SiCs apresentam inúmeras vantagens:

- O carbeto de silício faz parte da família dos componentes de grande gap. Ele possui uma banda de energia aproximadamente três vezes maior (3,26 eV) que para os componentes de silício (1,11 eV). Logo, eles são melhores isolantes;

- Os componentes de SiC possuem uma tensão de ruptura maior (>1200 V) que os de silício (em torno de 600 V);

- Uma outra vantagem importante é que os SiCs possuem uma resistência específica nitidamente inferior  $(0,3 \text{ m}\Omega \cdot cm^2)$  ao silício  $(400 \text{ m}\Omega \cdot cm^2)$ . [1]

Pelo fato de terem uma resistência específica mais baixa, os componentes de SiC apresentam uma menor perda por condução. Graças a uma corrente de recuperação mais baixa, observa-se também uma diminuição de suas perdas por comutação, permitindo assim a operação em frequências mais elevadas (>20 MHz). Com relação às características térmicas, a condutividade térmica do carbeto de silício é, aproximadamente, três vezes superior (4,9 W/cmK) que do silício (1,5 W/cmK). Logo, como a operação em ambientes severos implica, geralmente, no uso de sistemas de arrefecimento, os componentes de SiC apresentam um melhor resfriamento.

Na Fig. 2 pode-se ver o bom funcionamento dos componentes de grande gap. É válido destacar que os componentes de diamantes ainda são comercialmente inviáveis. [2]

Todas as características dos componentes de SiC contribuem para o alto investimento aplicado. O Laboratório IPES, como parte do grupo Safran, utiliza majoritariamente tais componentes por serem comercialmente viáveis e apresentarem ótimas características de operação.

Figura 1 – Resistência específica em função do comportamento de tensão.

Figura 2 – Temperatura máxima de junção em função da tensão de ruptura.

Fonte: Laboratório IPES.

Apesar de todos os pontos positivos, há ainda algumas dificuldades encontradas no uso dos SiCs, tais como: disponibilidade para compra no mercado, devido a sua comercialização para certas aplicações ser recente; preço um pouco elevado; instabilidade na tensão de limiar e problemas sobre a robustez do óxido metálico da porta dos MOSFETs em regime de avalanche e curto-cicruito.

Estas dificuldades destacam o problema da confiabilidade dos componentes de carbeto de silício. Neste contexto, a robustez é abordada de forma específica considerando

um possível melhoramento em sua análise frente aos MOSFETs. A área de operação segura que será estudada vai ser a do MOSFET SiC comercializado pela empresa CREE.

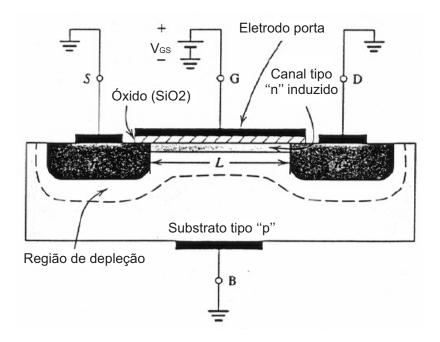

#### 2.2 Direção da Pesquisa Escolhida

O componente utilizado será o MOSFET CREE C2M0080120D (1200V, 80 m $\Omega$ ). O MOSFET é um componente unipolar e é comandado em tensão por meio de seu gate(porta) isolado. Este tipo de transistor MOS é dito como efeito de campo contituído de um substrato semicondutor (S) recoberto de uma fina camada isolante de óxido de silício (SiO2) de aproximadamente 0,1  $\mu$ m. [8]

O transistor MOSFET pode ser considerado como uma resistência variável. Os portadores majoritários (elétrons para um canal N) atuam no controle da passagem de corrente. Majoritariamente, os MOSFETs são dopados por o canal N, pois assim podem ser obtidas resistências de passagem mais baixas. De fato, como observa-se na Fig. 3 os diodos que aparecem na estrutura são apenas elementos parasitas, não veiculando a potência distribuída. [9]

Figura 3 – Esquema de camadas eletricamente dopadas em detalhe dos MOSFETs.

Fonte: Composants de l'électronique de puissance. Techniques de l'ingénieur.

É importante destacar que: a porta deste transistor é isolada por uma camada de óxido de silício e é levada a um potencial positivo com relação à fonte; ela repele as lacunas da zona P por um simples efeito eletrostático. Esta repulsão causa uma elevação inversamente proporcional do número de elétrons e um canal de portadores negativos é criado justamente em face da porta do MOSFET. A corrente elétrica pode passar por este canal, em direção ao dreno. A estado de bloqueio, a tensão inversa é principalmente suportada pela camada N<sup>-</sup>. Um transistor de alta tensão necessida de uma camada N<sup>-</sup> mais espessa e menos dopada, sendo mais resistiva. Há, portanto, um compromisso muito importante entre a resistência a estado passante e a tensão máxima suportada pelo componente a estado de bloqueio [10].

Pode-se constatar que entre as camadas  $N^+$  e a camada P, há uma formação de um diodo que impede a passagem de corrente direta da fonte em direção ao dreno, havendo falta de tensão porta-fonte. Este diodo é exatamente utilizável em um conversor, a condições de considerar sua rapidez, pois ele suporta muito bem a corrente nominal e a baixa carga que é armazenada nele (no caso de um MOSFET SiC).

# 2.3 Folha de Dados do MOSFET CREE C2M0080120D (1200V, 80 m $\Omega$ )

O datasheet, ou folha de dados, lista todas as características, além de alguns testes, do MOSFET utilizado. Com ela, pode-se obter os valores limites que se pode chegar de forma a não causar qualquer dano ao componente. Estes valores são úteis para construir a sua área de operação segura.

A Tabela 1 apresenta os valores máximos que não podem ser ultrapassados durante a manipulação, do contrário o componente será destruído. Estes parâmetros são dados a título de informação, pois os limites de danificação são levemente superiores.

| Símbolo         | Valor   | Unidade              | Condições do Teste                             |

|-----------------|---------|----------------------|------------------------------------------------|

| $I_{DS(DC)}$    | 31,6/20 | A                    | $V_{gs}$ =20 V, $T_c$ = 20 °C / $T_c$ = 100 °C |

| $I_{DS(pulse)}$ | 80      | A                    | Tempo de ruptura t<br>p = 50 $\mu \mathrm{s}$  |

| $V_{GS}$        | -10/+25 | V                    | -                                              |

| $P_{total}$     | 208     | W                    | $T_c = 25  ^{\circ}\mathrm{C}$                 |

| $T_j$           | 150     | $^{\circ}\mathrm{C}$ | -                                              |

Tabela 1 – Limites máximos de utilização.

As características elétricas são detalhadas na Tabela 2. Os fabricantes consideram uma boa margem sobre a tensão de avalanche (tensão de ruptura). Alguns ensaios realizados no Laboratório Ampère mostram que se pode elevar a tensão sobre o MOSFET até mais de 1700 V.

| Tabela 2 – | Características | elétricas | do MOSFET | estudado |

|------------|-----------------|-----------|-----------|----------|

|            |                 |           |           |          |

| Símbolo       | Mínimo | Máximo | Unidade            | Condições do Teste                               |

|---------------|--------|--------|--------------------|--------------------------------------------------|

| $V_{(BR)DSS}$ | 1200   | 1700   | V                  | $V_{GS} = 0V, I_{DS} = 100\mu A$                 |

| $V_{th}$      | 1,2    | -      | -                  | $V_{DS} = 10V, I_{DS} = 1mA, T_j = 150^{\circ}C$ |

| $R_{DS(on)1}$ | -      | 98     | $\mathrm{m}\Omega$ | $V_{GS} = 20V, I_{DS} = 1mA, T_j = 25^{\circ}C$  |

| $R_{DS(on)2}$ | -      | 208    | $\mathrm{m}\Omega$ | $V_{GS} = 20V, I_{DS} = 1mA, T_j = 150^{\circ}C$ |

As características térmicas podem ser vistas na Tabela 3.

| tabeia 3 – | Caracteristicas | termicas | ao | MOSFEI | estuaaao. |  |

|------------|-----------------|----------|----|--------|-----------|--|

|            |                 |          |    |        |           |  |

| Símbolo         | Parâmetros                                | Máximo | Unidade |

|-----------------|-------------------------------------------|--------|---------|

| $R_{\theta JC}$ | Resistência térmica junção-encapsulamento | 0,65   | K/W     |

| $Z_{\theta JA}$ | Impedância térmica junção-ambiente        | 40     | K/W     |

#### 2.4 Utilização de Dissipadores

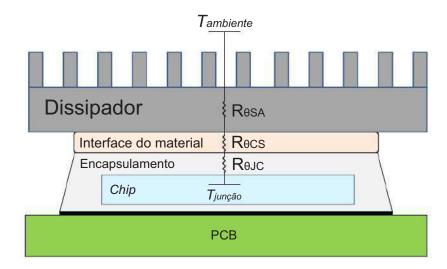

Um dissipador térmico é um componente metálico, geralmente de alumínio, que é utilizado para evitar que alguns componentes eletrônicos se aqueçam.

Quando um componente é atravessado por uma corrente elétrica, ele começa a se aquecer por efeito joule. Em alguns casos, é possível deixar que o componente se resfrie naturalmente ao ar livre (por convecção natural), mas há certas situações que o aquecimento pode levar ao equipamento sofrer uma ruptura térmica. Esta ruptura pode ser causada por: um embalamento térmico, a fusão da metalização do lado superior do transistor ou a fusão da base do componente.

O interesse do dissipador é de aumentar a superfície de contato do componente por permitir a evacuação mais rápida do calor. Para isso, ele deve estar em contato com o componente, atenuando suas perdas. Na Fig. 4 pode-se observar o fluxo térmico no módulo de potência que possui um *chip* de potência em seu interior, nota-se a geometria diferenciada do radiador (dissipador) e seu tamanho em relação aos outros componentes.

Figura 4 – Fluxo térmico em um módulo de potência.

Fonte: Composants de l'électronique de puissance. Techniques de l'ingénieur.

Para a escolha do dissipador utilizado nesse trabalho, serão seguidos os seguintes critérios:

• Análise do tamanho apropriado à aplicação. Sabe-se que o preço do dissipador aumenta com o seu tamanho;

- A forma do dissipador é igualmente importante. Será escolhido um equipamento que a forma seja próxima ao componente, evitando problemas de incompatibilidade;

- Além disso, é importante escolher um dissipador que possua um coeficiente térmico que se aproxime do componente.

Para este trabalho foram testados 3 tipos diferentes de dissipadores, permitindo analisar o impacto sobre a área de operação segura e, também, a atenuação de degradações que incidem sobre o MOSFET do módulo de potência.

# 3 Fundamentação Teórica

## 3.1 Estado da Arte sobre a Área de Operação Segura dos MOS-FETs

Este estudo permitirá compreender as razões para estudar a área de operação segura dos semicondutores. Além disso, será possível concluir algumas definições sobre os parâmetros importantes e os elementos necessários para definir a área de operação segura, garantindo a proteção do sistema eletrônico.

#### 3.1.1 Estudo da Característica de Saída do MOSFET

Esta característica traduz a dependência da corrente do dreno  $(I_DS)$  em função da tensão porta-fonte  $(V_{GS})$ . Como pode ser visto na Fig. 5, o MOSFET é constituído de 4 eletrodos: gate (porta), drain (dreno), source (fonte) e substrato. A fonte e o substrato são religados por um mesmo eletrodo na maioria dos casos, além de que o dreno é mantido sempre sob uma tensão positiva em relação à fonte. Quando uma tensão positiva é aplicada à porta, uma corrente circula lateralmente do dreno para a fonte, através de uma região chamada de canal, com comprimento L que varia de 0,5 à 10  $\mu$ m) e largura (1 à 500  $\mu$ m). [8]

Figura 5 – Princípio de funcionamento do MOSFET do tipo N.

Fonte: Les Transistors à Éffet de Champ  $\operatorname{MOS}$  - Centrale Marseille.

Quando se aplica uma tensão positiva entre a porta e a fonte, um campo elétrico é criado pela tensão  $V_{GS}$  e empurra os portadores majoritários presentes no substrato. Este último, sendo do tipo P, possui como portadores majoritários as lacunas. Então, logo abaixo da porta é formada uma zona de depleção, vazio de portadores livres (lacunas). Paralelamente, a tensão positiva atrai um conjunto de elétrons provenientes da fonte e do dreno (onde eles são majoritários). Quando um número suficiente de elétrons se acumula na superfício do canal, sob a porta, uma zona do tipo N é efetivamente criada. A partir daí, uma corrente elétrica se estabelece atraversando a zona N induzida do dreno em direção à fonte. A zona N induzida forma um canal N que dá nome ao tipo do MOSFET (um transistor do tipo N é realizado sobre um substrato do tipo P). [11]

O valor da tensão porta-fonte  $V_{GS}$  correspondente à acumulação suficiente de elétrons para criar um canal condutor é chamada de tensão limiar  $(V_{th})$ . A porta e o substrato (religado à fonte) formam um capacitor cujo dielétrico é a camada de óxido metálico da porta. A tensão  $V_{GS}$  aplicada provoca a carga deste capacitor com acumulação de cargas positivas sobre a porta e de cargas negativas na zona de inversão que forma o canal. É, portanto, esta tensão que controle a condutividade do canal e a corrente que circula quando uma tensão positiva é aplicada.

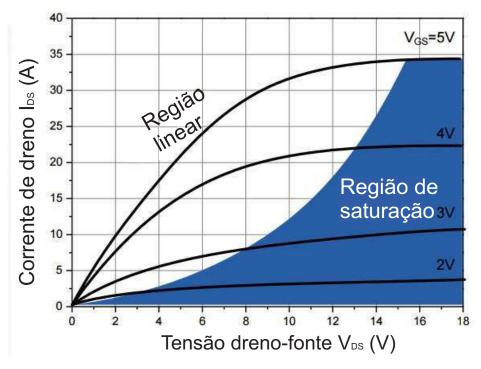

Figura 6 – Característica de saída do MOSFET.

Fonte: Fairchild Semiconductor Corporation, AN 4161.

Para determinar a importância da área de operação segura, a característica de saída do MOSFET foi estudada em diversas aplicações [9]. A Fig. 6 mostra que esta característica é delimitada por duas zonas: uma região linear ou ôhmica e uma região de saturação. A região linear é chamada de região ôhmica porque o MOSFET se com-

porta como uma resistência, a corrente no dreno é diretamente proporcional à tensão dreno-fonte. Isso implica que mesmo para baixos valores de tensão porta-fonte, a corrente aumenta consideravelmente quando se altera o valor de  $V_{DS}$ . O limite entre a zona ôhmica e a zona de satuação é definido pela característica:  $V_{DS} \leq V_{GS} - V_{th}$ . [12] [3]

A corrente  $I_{DS}$  pode ser regulada pela tensão  $V_{GS}$  quando se está na região ôhmica, diz-se assim que o MOSFET opera em modo de funcionamento linear. Este modo requer bastante atenção quanto à potência dissipida (devido aos altos valores de corrente e tensão).

É, portanto, importante definir um diagrama que permita saber se, para um conjunto  $(V_{DS}, I_{DS})$  dado, o componente poderá operar sem ultrapassar os valores definidos pela folha de dados [8]. Este diagrama,  $I_{DS} = f(V_{DS})$  é chamado de área de operação segura do componente.

#### 3.1.2 Área de Operação Segura

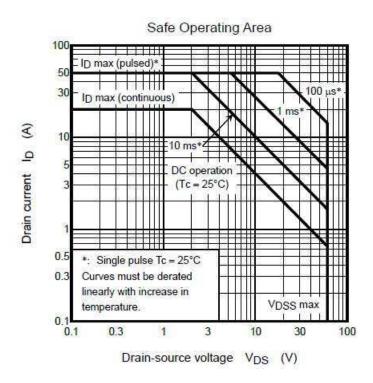

A forma da curva de operação segura, de maneira geral, define os limites para o bom funcionamento do MOSFET. Ultrapassando tais limites, pode-se surgir efeitos danosos ao componente. A SOA característica de um MOSFET pode ser vista em Fig. 7. [10] [11] [13]

Figura 7 – Típica curva SOA para um MOSFET de potência. Fonte: Fairchild Semiconductor Corporation, AN 4161.

Esta clássica curva de operação segura apresenta 4 limites essenciais:

(A) Limite em curto-circuito;

- (B) Limite a estado passante;

- (C) Limite em potência;

- (D) Limite em avalanche;

As curvas descrevem a evolução da corrente de dreno em função da tensão drenofonte. É válido ressaltar que a curva apresentada é apenas ilustrativa, pois em termos práticos existem outros fatores que influenciam na definição dos limites. Um bom exemplo é o encapsulamento do componente que, apresentando qualquer imperfeição, pode alterar a condutividade térmica, modificando o formato da curva.

Em (A), visto na Fig. 7  $R_{DS}$  é o limitante que estabelece a dependência entre  $V_{DS}$  e  $I_{DS}$ . O declive da linha é simplesmente o máximo valor para  $R_{DS(on)}$  em uma dada condição de operação do MOSFET. A equação (3.1) mostra esta relação.

$$I_{DS} = \frac{V_{DS}}{R_{DS(on)}} \tag{3.1}$$

Seguindo o limite definido em (A), chega-se ao estágio (B) que é limitado pela corrente máxima que o encapsulamente do componente pode suportar, assim a quantidade de corrente será fortemente dependente do tipo de encapsulamento utilisado. Desde o tamanho do *chip*, até o esquema de conexão entre os componentes irão afetar a nível deste limitante. Atualmente, há diversos estudos na área buscando estabelecer a máxima passagem de corrente e o mínimo efeito indutivo parasita. [14]

Em (C), observa-se o limite de potência. Ele é calculado tendo em vista a máxima potência que o sistema é permitido alcançar, mantendo-se estável, para uma dada temperatura. As equações (3.5), (3.3) e (3.4) traduzem matematicamente a curva limite. [6]

$$P_{dissipada} = P_{aerada} \tag{3.2}$$

$$T_{i} = T_{amb} + Z_{thic} \cdot P_{dissipada} \tag{3.3}$$

$$I_{DS} = \frac{\Delta T_{max}}{Z_{\theta(t_{mulse})} \cdot V_{DS}} \tag{3.4}$$

As equações ilustram algumas dependências importantes:

• A  $I_{DS}$  depende da máxima temperatura admissível para o valor de junção do componente;

- O valor da corrente de dreno é influenciado pelo valor da impedância térmica sob efeito pulsado. Para pulsos pequenos de corrente, o valor desta impedância depende da largura dos pulsos e do ciclo de trabalho;

- Devido ao aumento da dissipação de potência com  $V_{DS}$ , o valor de  $I_{DS}$  também depende inversamente da tensão aplicada sobre o componente.

Em (D), é estabelecida a máxima tensão de ruptura para o componente. Violando este valor, qualquer corrente ou tensão aplicada sobre o MOSFET levará-lo à destruição total.

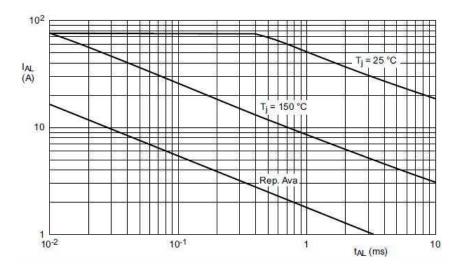

Para os semicondutores da NXP, pode-se ver em Fig. 8 a influencia da área de operação segura em função da temperatura de junção. Quando se trabalha em regime de avalanche pulsado, a corrente de dreno  $I_{AL}$  diminui com a temperatura de junção e o número de impulsos [13]. Isso, possibilita deduzir que a área de operação segura, mais precisamente o limite de potência, decresce com a temperatura de junção e o número de impulsos.

Figura 8 – Influciência da corrente de dreno em função da temperatura de junção e do regime pulsado.

Fonte: Fairchild Semiconductor Corporation, AN 10273.

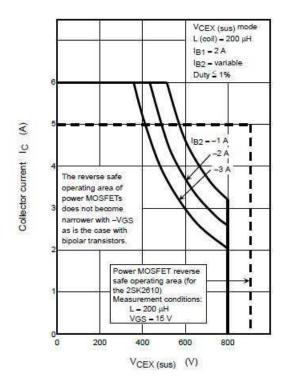

Para os transistores, dependendo de seu estado de abertura ou fechamento, definese duas áreas de operação segura: a FBSOA e a RBSOA.

A FBSOA é estabelecida quando do momento de circulação de corrente no transistor ao estado passante. Como pode-se ver em Fig. 9, a área de operação segura definida para operação DC e pulsada.

A RBSOA, Fig. 10, é definida como a SOA durante o breve intervalo de tempo antes da abertura total do transistor - durante este pequeno espaço de tempo a corrente

Figura 9 – Área de operação segura para um MOSFET de potência.

Fonte: Toshiba Leading Innovation.

Figura 10 – Área de operação segura reversa para um MOSFET de potência.

Fonte: Toshiba Leading Innovation.

de base é reversa. Quando o dispositivo é usado no campo do chaveamento de potência em aplicações para fontes de alimentação, por exemplo, a carga torna-se indutiva.

Os semicondutores são submetidos a uma forte influência da temperatura com

bom risco de aparição de pontos com temperatura anormal nas intermediações do componente. Este fenômeno afeta consideravelmente a robustez dos componentes de potência e, portanto, o rendimento das aplicações nas quais eles são utilisados.

O conceito de densidade de potência vem sendo trabalhado cada vez mais, daí, a necessidade de manter a temperatura de operação de um módulo de potência dentro de um limite seguro. Os dissipadores, ou radiadores, são bastante utilisados e serão analisados do ponto de vista da influência sobre a área de operação segura do MOSFET de potência.

De forma geral, as aplicações utilisam a FBSOA como curva característica geral, logo ela será trabalhada visto que o objetivo desta pesquisa é compreender o funcionamento do MOSFET a estado passante, além de analisar a influência da temperatura sobre a curva de potência. É válido destacar que a parte DC, vista na Fig. 9, será desconsiderada, pois para os MOSFETs de carbeto de silício ela é inexistente devido ao componente ser dotado de uma elevada condutividade térmica que favorece o seu resfriamento natural.

#### 3.2 Resfriamento do MOSFET SiC

Nesta parte, será detalhada a teoria utilisada para descrever o método que irá possibilitar traçar a curva de operação segura para o MOSFET CREE (1200 V, 80  $m\Omega$ ). Em seguida, será apresentada uma melhoria para o modelo.

Durante a manipulação dos componentes, percebe-se que são as perdas de potência que provocam a dissipação de calor e, portanto, o aumento da temperatura de junção. Para evitar ultrapassar os valores máximos fornecidos pela folha de dados, pode-se utilisar um dissipador térmico cuja escolha de um tamanho adequado é de extrema importância para evitar possíveis perdas. [15]

Para a aplicação prática deste trabalho, utilisou-se três formas de resfriamento: resfriamento ao ar livre, dissipador a aletas e à placa de água. A partir daí, pode-se traçar três regiões seguras e realizar a superposição delas , analisando os fatores que influenciam sobre a SOA em função do tipo de dissipador escolhido.

O esquema da montagem de um chip de potência montado em um módulo sobre um dissipador pode ser visto na Fig. 11.

Existe uma forte analogia térmica-elétrica entre as grandezas usuais (tensão, intensidade, temperatura, potência, resistência e outras). Esta analogia pode ser vista na Tabela 4.

Esta analogia permite definir uma resistência total junção-ambiente do sistema representado na Fig. 11

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CS} + R_{\theta SA} \tag{3.5}$$

Figura 11 – Diagrama para a resistência térmica de um dispositivo com dissipador de calor.

Fonte: Heat Sink Selectino Guide fot Thermally Enhanced SO8-FL.

Tabela 4 – Analogia entre as grandezas térmicas e elétricas.

| Grandezas Térmicas                 | Grandezas Elétricas        |

|------------------------------------|----------------------------|

| T: Temperatura                     | U: Tensão Elétrica         |

| $R_{\theta}$ : Resistência Térmica | R: Resistência Elétrica    |

| $Z_{\theta}$ : Impedãncia Térmica  | Z: Impedância Elétrica     |

| $C_{\theta}$ : Capacidade Térmica  | C: Capacitância Elétrica   |

| P: Calor ou Potência Térmica       | I: Intensidade de Corrente |

Um modelo equivalente será concebido ao componente montado sobre o dissipador de calor. Este permitirá obter as equações que irão caracterizar a diferença de temperatura entre os diferentes elementos que influenciam no método de traçado da curva SOA.

#### 3.3 Modo de Funcionamento do MOSFET

Com respeito ao modo de funcionamento do MOSFET, pode-se definir dois regimes: estágio e dinâmico. A aplicação vista em [13] considera dois tipos de funcionamentos em regime dinâmico, segundo a frequência de impulsão aplicada à fonte:

- Pulso único: o fenômeno se produz uma só vez de maneira involuntária durante um tempo  $t_p$ ;

- Pulso repetitivo: o fenômeno se produz várias vezes de maneira repetitiva durante um tempo  $t_p$  por um período de tempo T. Será este caso estudado na prática.

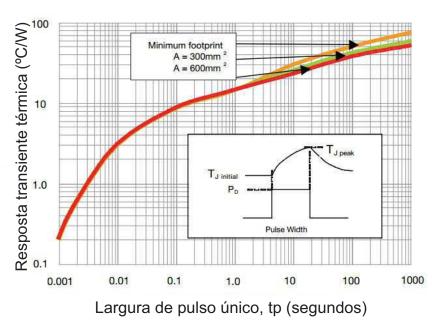

É importante conhecer a forma que evolui a temperatura de junção em função da potência dissipada, ou seja, se é aplicado um impulso à potência constante. Durante um tempo  $t_p$ , correspondente ao tempo de destruição do componente, aplica-se um degrau de potência  $P_0$  e se analiza a resposta em temperatura do sistema. O fato de aproximar a temperatura de junção àquela que se deseja trabalhar, permite dimensionar ou escolher o dissipador de calor adequado para o sistema [15] e [16].

Figura 12 – Transiente de resposta térmica do sistema.

Fonte: NXP Thermal Analysis of Semiconductor Systems.

#### 3.3.1 Determinação da Impedância Térmica Junção-encapsulamento

Paro o caso de modelar o sistema em regime dinâmico, é necessário considerar a impedância térmica do componente.

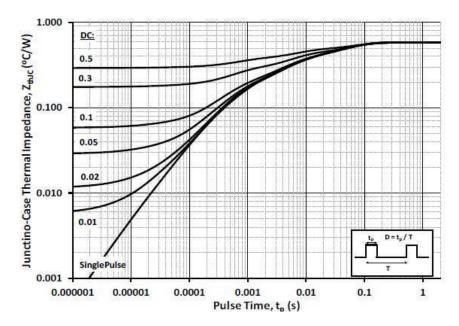

A resistência térmica junção-encapsulamento do MOSFET CREE é fornecida pelo fabricante na folha de dados, porém para a impedância térmica, que é função do tempo de destruição do transistor e do ciclo de trabalho, é preciso analisar a Fig. 13 na folha de dados [8].

Para o caso de trabalhar a uma frequência f=10KHz e um ciclo de trabalho D=0,5, encontra-se um tempo de ruptura (ou quebra) de  $t_p=500\mu s.$

No caso de pulso único (Single Pulse, no gráfico), para um  $t_p = 500 \mu s$  obtémse um valor aproximado para a impedância térmica junção-encapsulamento de:  $Z_{\theta JC} = 0,12 \, {}^{\circ}C/W$ . No caso de um pulso repetitivo, considerando a curva de ciclo de trabalho 0,5 na Fig. 13, obtém-se um valor:  $Z_{\theta JC} = 0,34 \, {}^{\circ}C/W$ .

Figura 13 – Impedância térmica em função do tempo de quebra do MOSFET.

Fonte: Folha de Dados CREE C2M0080120D.

#### 3.3.2 Modelagem Térmica

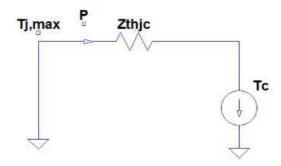

A analogia entre as grandezas elétricas e térmicas do sistema, vista na Fig. 11, permite igualmente representar como um circuito elétrico. Há três métodos matemáticos para determinar o circuito equivalente a partir da equação de calor. Estes métodos podem ser encontrados em [6].

Para a modelagem estática, cada componente é associado a uma resistência, considerando as temperaturas de entrada e saída do sistema, Fig. 14.

Figura 14 – Modelagem térmica do sistema em estado estático.

Fonte: Choosing a Thermal Model for Electromechanical Simulation of Power Semiconductors Devices.

Considerando a modelagem dinâmica, deve-se levar em conta a impedância térmica junção-encapsulamento. Apenas esta grandeza é fornecida na folha de dados do componente.

Graças à modelagem térmica, é possível extrair as relações matemáticas entre a temperatura de junção e a temperatura ambiente usando da "lei de Ohm". Trabalhando a grandeza de corrente, como sendo a potência total, e a tensão, sendo a diferença de

Figura 15 – Modelagem térmica do sistema em estado dinâmico.

Fonte: Choosing a Thermal Model for Electromechanical Simulation of Power Semiconductors Devices.

temperatura, pode-se chegar às relações fundamentais em comportamento estático (3.6), e em comportamento dinâmico (3.7). Usando de tais equações, será possível construir o limite de potência para a definição da área de operação segura.

$$T_i = T_a + (R_{\theta JC} + R_{\theta CS} + R_{\theta SA}) \cdot P_{tot} = R_{\theta JA} \cdot P_{tot}$$

(3.6)

$$T_{j,max} = T_c + (Z_{\theta JC}) \cdot P_{tot} = R_{\theta JA} \cdot P_{tot}$$

(3.7)

#### 3.4 Influência do Tipo de Dissipador Térmico

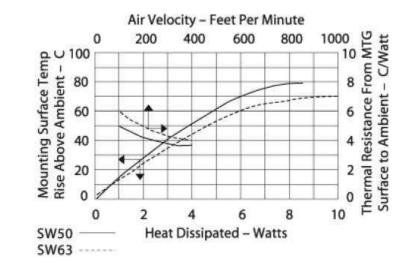

Para o caso prático, serão utilizados três tipos de dissipadores térmicos. Além disso, uma análise de seu impacto sobre a resistência térmica total será realizado em regime estático.

Cada dissipador possui uma  $R_{\theta SA}$  diferente, de tal forma que a resistência total  $R_{\theta JA}$  do sistema irá mudar seu valor em função do dissipador utilizado. A resistência térmica da pasta térmica pode ser encontrar na referência [17]. O valor utilizado será de:  $R_{\theta CS} = 0, 1$  °C/W. Para a resistência térmica junção-encapsulamento, tem-se:  $R_{\theta JC} = 0, 6$  °C/W. Este valor pode ser encontrado na folha de dados do componente. A temperatura de junção é dada por:  $T_j = 150$  °C e a temperatura ambiente  $T_a = 25$  °C.

Para o caso do resfriamento ao ar livre, o componente não apresenta boa eficiência. O risco de ultrapassar a temperatura de junção máxima é bem elevado, pois se há um aquecimento local no componente, ele irá dissipar toda a energia. É esperado, portanto, que a resitência térmica seja substancialmente elevada. Consultando a folha de dados para o MOSFET CREE deste trabalho, pode-se obter uma resistência térmica máxima total junção-ambiente de:  $R_{\theta JA(ar)} = 40 K/W$ .

A utilização de um dissipador a aletas tem como base o ar funcionando como vetor de extradição. A transferência de calor se faz por convecção. O número das aletas utilizado

é importante porque define a superfície do dissipador escolhido. Uma superfície grande implicará em um aumento da resistência térmica.

Os dados de cálculo que seguem são necessários para calcular a resistência térmica do dissipador a aletas:

- $R_{DS(on)} = 80m\Omega;$

- $R_{\theta JC} = 0.6 \, {^{\circ}C/W};$

- $T_i = 150 \, ^{\circ}C;$

- $T_c \approx T_s \ (R_{\theta CS} \ \text{baixo});$

- $I_{DS(DC)} = 31, 6A;$

Agora, para determinar a resistência do dissipador faz-se necessário conhecer a potência dissipada para que se calcule a temperatura do dissipador  $(T_s)$ . A estimação das perdas é mostrada na equação (4.1).

$$P = R_{DS(on)} \cdot I_{DS(DC)}^2 = 79,9W \tag{3.8}$$

Seguindo o cálculo, para a estimação da temperatura do encapsulamento podese realizar a extrapolação da curva dada na Fig. 3.4. Assim, pode-se alcançar o valor  $T_c \approx 90~^{\circ}C$ .

Figura 16 – Determinação da resistência térmica para um dissipador a aletas.

Fonte: Folha de Dados Dissipador a Aletas T0-247.

A temperatura de junção para este cenário é calculada na equação (3.9). Percebese que seu valor é inferior à 150 °C ( $T_{j,max}$  da folha de dados), logo a estimação sobre a temperatura  $T_c$  é válida.

$$T_j = T_c + (R_{\theta JC}) \cdot P_{tot} = 137,94 \,^{\circ}C$$

(3.9)

O cálculo da resistência do dissipador a aletas é mostrado na equação (3.10).

$$T_s = T_a + (R_{\theta SA}) \cdot P_{tot} \rightarrow R_{\theta SA} \approx 0.8K/W$$

(3.10)

Logo, pode-se chegar, finalmente, ao cálculo da resistência térmica total junçãoambiente na equação (3.12)

$$R_{\theta JA(aletas)} = R_{\theta JC} + R_{\theta CS} + R_{\theta SA} = 0, 6 + 0, 1 + 0, 8 = 1, 5K/W$$

(3.11)

Para o caso do resfriamento utilizando uma placa de água, tem-se que a resistência térmica dissipador-ambiente  $R_{\theta CS}$  é bem pequena, de forma que será tomada uma aproximação de  $R_{\theta SA} \approx 0,1 K/W$  para a resistência dissipador-ambiente. Logo, a resistência junção-ambiente será:

$$R_{\theta JA(aqua)} = R_{\theta JC} + R_{\theta CS} + R_{\theta SA} = 0, 6 + 0, 1 + 0, 1 = 0, 8K/W$$

(3.12)

# 4 Plotagem da Área de Operação Segura do MOSFET SiC CREE

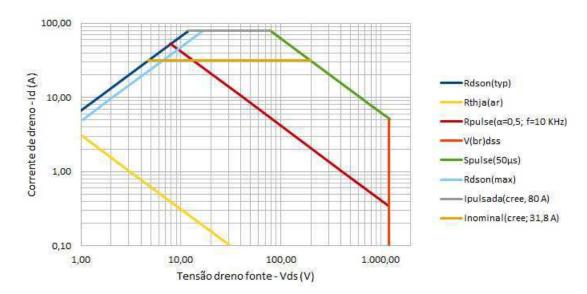

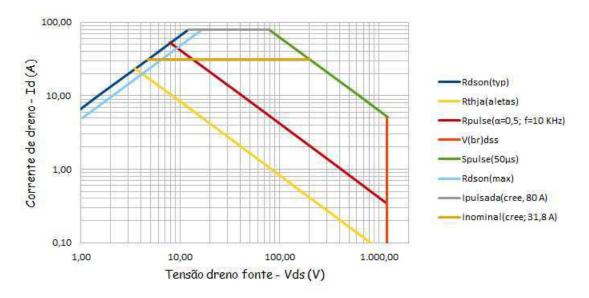

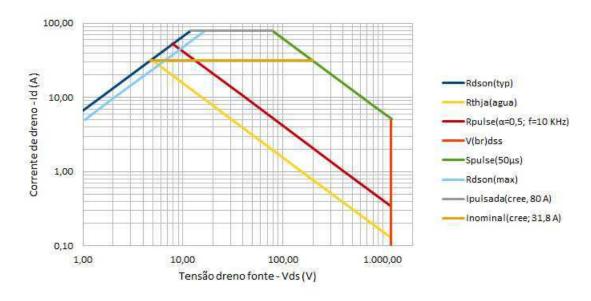

Nesta parte será traçada a área de operação segura para o MOSFET SiC CREE C2M008012D (1200 v,  $80\text{m}\Omega$ ) com encapsulamento TO-247, para cada dissipador, a fim de estudar sua influência sobre a proteção do componente. As condições de operação para o caso estudado foi de:  $V_{GS}=20V, f=10kHz$  e D=0,5.

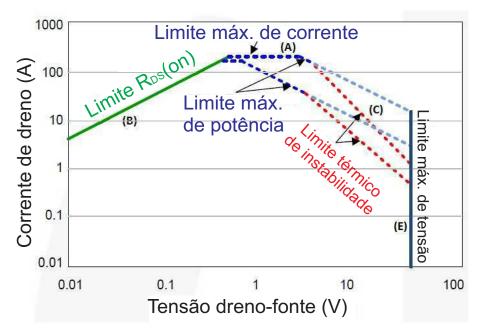

#### 4.1 Método Utilizado para o Traçado da SOA

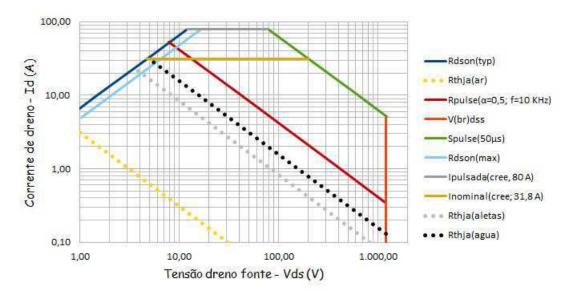

Para explicar o método de plotagem da SOA do componente em estudo, pode-se tomar como a base as curvas geradas na Fig. 17 correspondentes ao caso do resfriamento ao ar livre. Para construção de cada limite, as devidas equações foram implementadas utilizando os valores encontrados no datasheet do componente. Na Fig. 17 pode-se ver a SOA para o caso do MOSFET associado com resfriamento ao livre.

Figura 17 – Área de Operação Segura com resfriamento ao ar livre.

O primeiro limite definido é o limite a estado passante. Este, corresponde ao funcionamento do MOSFET ao estado passante e o componente se comporta como uma resistência. Na Fig. 17 há dois traços:  $R_{dson(typ)}$  e  $R_{dson(max)}$ . Há uma relação linear, equação (4.1), que associa a corrente de dreno  $I_{DS}$  e a tensão dreno-fonte  $V_{DS}$ .

$$V_{DS} = I_D \cdot R_{DS(in)} \ (T_{i,max}; V_{GS} = 20V)$$

(4.1)

Para o SOA traçada foram utilizados dois valores de resistência específica  $R_{DS(on)}$ : o caso típico  $(0, 15\Omega)$  e o caso máximo  $(0, 18\Omega)$  fornecidos no datasheet.

Percebe-se que a área de operação segura diminui com o aumento da resistência específica. Isso pode ser explicado pelo fato que aumentar a resistência específica implica em elevar as perdas por condução no compoente e, portanto, o fato de haver a regulação na tensão  $V_{DS}$ , com  $V_{GS}$  fixo, conduzirá a uma corrente mais baixa.

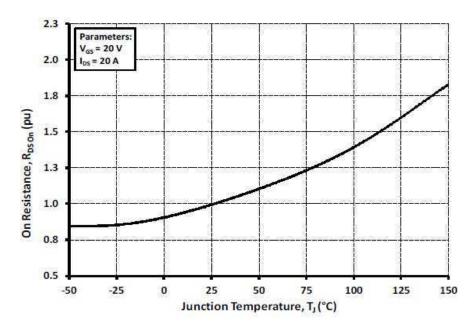

A determinação da resistência específica em aplicações de eletrônica de potência foi bastante estudada pelo fabricante Infineon em suas aplicações [3]. Pode-se, portanto, determiná-la de duas maneiras: estudando a evolução da resistência em função da corrente de dreno ou apoiando-se sobre a dependência  $R_{DS(on)}$  com relação à temperatura, Fig. 18. Em seguida, determina-se o coeficiente  $\alpha$  na equação (4.3).

Figura 18 – Relação entre a resistência de passagem normalizada e a temperatura de junção.

$$R_{DS(on)}(T_j) = R_{DS(on)}(25 \, ^{\circ}C) + \left(1 - \frac{\alpha}{100}\right)^{T_j - 25}$$

(4.2)

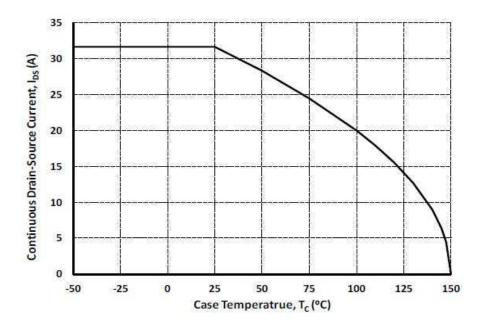

Para o limite de curto-circuito, dois valores foram utilizados:  $I_{nominal} = 31,6A$  e  $I_{pulsada} = 80A$ . A corrente de impulso é medida pelo fabricante com um tempo de  $50\mu s$  para destruição do componente, em uma temperatura de 25 °C. Este valor de corrente corresponde a aproximadamente 2,5 vezes a corrente nominal. O método de cálculo para a corrente nominal se utiliza da equação (3.6) considerando as perdas dissipadas à temperatura de junção máxima  $(P = R_{DS(on)}(T_{j,max}) \cdot I_{DS(DC)}^2)$ . Assim, obtém-se a equação (4.3). A Fig. 19 mostra a relação da corrente com a temperatura de junção.

Figura 19 – Corrente nominal em função da temperatura de junção.

$$I_{DS}(Tc) = \sqrt{\frac{(T_j - T_c)/R_{\theta JC}}{R_{DS(on)}(T_{j,max})}}$$

$$\tag{4.3}$$

Passando para limite em avalanche, a tensão de ruptura (destruição) do componente é de 1200V ( $V_{(BS)DSS}$ ). Acima deste limite, será observado o fenômeno da avalanche: o campo elétrico no interior do material é suficientemente grande para acelerar os elétrons até o ponto que eles se desprendem dos átomos. O número de elétrons livres irá aumentar rapidamente causando a liberação de mais outros, formando uma reação em cadeia.

Para o limite de potência, geralmente associado com a forma de aplicação do teste e com o encapsulamento, apresenta-se na Fig. 17 três traços inclinados:

- $S_{vulse}(50\mu s)$ : cálculo realizado com impulso único de  $50\mu s$ ;

- $R_{pulse}$ : o impulso de corrente é repetitivo e com parâmetros ( $\alpha = 0, 5; f = 10KHz$ ).

- $R_{thja}(ar)$ : limite estabelecido para o caso de resfriamento ao ar livre, considerante a operação em regime permanente.

A partir da região de operação segura plotada, considerando que haverá um resfriamento natural ao ar livre para o módulo, percebe-se claramente que o limite principal que definirá a SOA será estabelecido pela operação de resfriamento. Neste caso analisado, não foi implementado nenhum dissipador, fazendo com que o limite de funcionamento da resistência térmica junção-ambiente formasse uma área bem restrita. Daí, a necessidade de, para grandes aplicações de eletrônica de potência, utilizar-se de dissipadores.

#### 4.2 Comparação das SOAs em Função do Tipo de Resfriamento

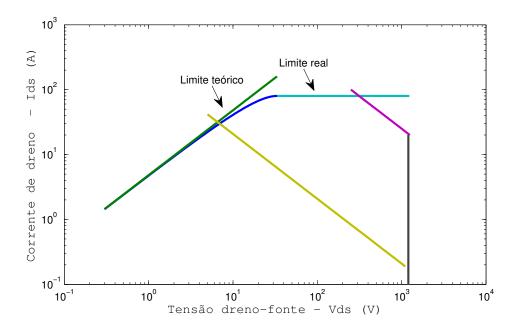

Na Fig. 20 pode-se visualizar a SOA para o caso do sistema utilizar um arrefecimento a aletas, e na Fig. 21 a região de operação para um dissipador com uma placa de água.

Figura 20 – Área de Operação Segura do componente com um dissipador a aletas.

Figura 21 – Área de Operação Segura do componente com uma placa de água.

Comparando as 3 SOAs, todas as curvas permanecem inalteradas, exceto a curva de potência em regime permanente. Isso implica que o dissipador influciencia a SOA apenas a nível de potência em regime estático. Isso pode ser explicado pelo fato que adicionando um dissipador, apenas a resistência total do sistema é alterada, porém, a tensão de avalanche, resistência específica e corrente nominal permanecem com o mesmo

valor. Analisando a Fig. 22 percebe-se, claramente, que a área de operação segura aumenta ao passo que a resistência térmica total diminui: uma baixa resistência térmica permite uma melhor troca de calor.

Figura 22 – Superposição das Áreas de Operação Segura para o resfriamento ao ar livre, a aletas e utilizando um dissipador com placa de água.

# 4.3 Aproximação Não-linear para Plotagem da Área de Operação Segura

Como pode ser vista na Fig. 22, a área de operação segura que foi traçada é descrita por limites lineares. Para construção do modelo, foram utilizados dados obtidos do datasheet e algumas equações encontradas nas aplicações que descrevem o comportamento do MOSFET.

Contudo, analisando as características de saída do MOSFET, dada na Fig. 6, constata-se que a estado passante e para o limite de curto circuito, as curvas são levemente inclinadas. Há uma modelagem do transistor MOSFET realizada na tese de doutorado [17] que propõe um modelo matemático para representar adequadamente as características do MOSFET em regime linear e saturado, considerando dois parâmetros (transcondutâncias  $K_{plin}$  e  $K_{psat}$ ).

Para a equação de corrente  $I_{DS}$ , tem-se (4.4), daí, pode-se deduzir também a equação para a resistência específica (4.5).

$$I_{DS} = K_{plin}(V_{GS} - V_{th}) \cdot V_{DS} - \frac{K_{plin} \cdot V_{DS}^2}{2 \cdot K_{nsat}}$$

, se  $V_{DS} \leq (V_{GS} - V_{th}) \cdot \frac{K_{psat}}{K_{nlin}}$  (4.4)

$$R_{DS(on)} = \frac{1}{\frac{\partial I_{DS}}{\partial V_{DS}}(V_{DS} = 0, V_{GS})} = \frac{1}{K_{plin}(V_{GS} - V_{th})}$$

(4.5)

Na região região de saturação, a corrente é definida pelo modelo matemático:  $\frac{\partial I_{DS}}{\partial V_{DS}}=0$ . Assim, usando a equação 4.4, obtém-se (4.6).

$$V_{DS(sat)} = (V_{GS} - V_{th}) \cdot \frac{K_{plin}}{K_{psat}}$$

$$(4.6)$$

Utilizando a equação (4.6) e (4.4), pode-se obter a expressão para a corrente de dreno em saturação (4.7).

$$I_{DS(sat)} = \frac{K_{psat}}{2} (V_{GS} - V_{th})^2 \quad , \text{ se } V_{DS} \leqslant (V_{GS} - V_{th}) \cdot \frac{K_{psat}}{K_{plin}}$$

(4.7)

Estes dois novos modelos permitem representar uma nova área de operação segura que pode ser vista na Fig. 23.

Figura 23 – Aproximação não-linear para a SOA do MOSFET de SiC.

Este modelo é, portanto, mais realista que a área de operação segura plotada anteriormente. Como pode ser visto na Fig. 23, os limites para a zona ôhmica e a estado passante possuem uma leve inclinação. Este modelo melhorado foi realizado de tal sorte que os limites se coindicem.

# 5 Análise da Robustez do MOSFET

#### 5.1 Novos Conceitos

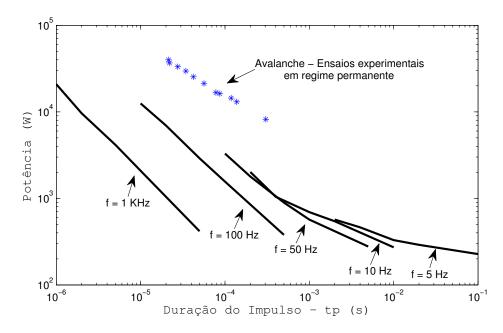

Por meio dos limites representados na área de operação segura do MOSFET, define-se o limite em potência, ou em temperatura. Em regime pulsado, o tempo para destruição do componente  $t_p$  intervém na área de operação segura clássica fornecida, daí, a importância de avaliar a SOA do componente submetendo-o a testes de sobretenção e sobrecorrente.

Estabelecendo uma temperatura de junção máxima  $(T_{j,max})$ , a impedância térmica depende do tempo de destruição do transistor e do ciclo de trabalho. A equação (3.7) mostra a dependência da potência dissipada em função do tempo de ruptura, dessa forma, pode-se definir um limite para a área de operação segura. [18] [19]

Para implementação do algoritmo, em ambiente Matlab, definiu-se alguns valores para o ciclo de trabalho constante (contidos no datasheet), fazendo variar o tempo de quebra para diferentes frequências (5 Hz à 1 KHz). No datasheet do componente utilizado neste trabalho há diferentes curvas, com ciclo de trabalho constante, relacionando a impedância térmica de junção e o tempo de quebra. Um vetor de valores para tempo de quebra foi gerado utilizando estas curvas, em seguida, supondo regime de pulso único, pode-se obter as impedâncias térmicas e, por fim, com ajuda da equação (3.7), calcula-se a potência associada para cada valor do vetor de tempo de quebra.

No mesmo gráfico, representa-se também uma série de ensaios de ruptura em avalanche realizados em conjunto com a equipe do Laboratório Ampère. Foram representadas curvas de energia em função do tempo de ruptura do componente para o MOSFET CREE. Para o experimento, foi imposto por várias vezes um tempo de avalanche suficientemente longo com uma tensão de 2000V e, assim, observado a evolução da energia de avalanche até a ruptura total. [18]

Finalmente, um ensaio em curto-circuito foi, também, estudado. Este ensaio foi realizado por Cheng Chen [21] que estudou a robustez dos MOSFET SiC em curto-circuito. A ruptura observada é um curto-circuito físico entre o dreno e a fonte, com uma energia  $E_j=714mJ$  durante  $12,5\mu s$ .

As diferentes modelagens e ensaios podem ser vistos na Fig. 24.

A variação de potência para diferentes frequências apresenta-se de forma coerente. Para um tempo de excitação dado, a potência diminui com a frequência porque é fornecido menos energia para resfriar o componente.

Figura 24 – Área de operação segura em potência-tempo para diferentes ensaios.

Os ensaios de avalanche mostram também que fornecendo potências maiores haverá uma diminuição do tempo de destruição do MOSFET de potência. Daí, há uma redução do limite de potência, visto que a temperatura de junção do componente torna-se cada vez mais elevada, considerando o limite físico do dissipador acoplado ao MOSFET SiC.

#### 5.2 Robustez do Transistor MOSFET

Os conversores de potência são submetidos a efeitos de curto-circuito durante sua vida útil, tornando importante o estudo da robustez do MOSFET durante o regime de operação.

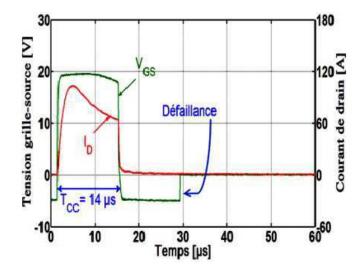

Alguns ensaios mostram que o MOSFET SiC é capaz de manter por  $13\mu s$  o estado de curto-circuito sob uma tensão dreno-fonte de 600V, especificamente entre 13 e  $80\mu s$ . Nestas condições, surge um forte aumento das correntes de fuga a nível da porta e do dreno. Além disso, o aumento das correntes de fuga implica a elevação da resistência específica, aumentando as perdas por condução. Outro fenômeno importante é a tensão porta-fonte, também afetada como pode ser visto na Fig. 25. [19] [20]

A Fig. 25 é o resultado de um ensaio repetitivo em curto-circuito (aumenta-se cada vez em um microssegundo) até  $T_{cc}=14\mu s$  onde o MOSFET SiC assegura a abertura da corrente de curto-circuito. Pode-se definir uma energia crítica Ec que será a energia para haver o primeiro curto. Um outro fenômeno responsável pelo aumento dos curtos-circuitos, logo da degradação dos MOSFETs, surge da tensão limiar  $(V_{th})$ . De fato, segundo [21], em algumas situações há a criação de cargas adicionais sobre a interface do SiO2, provocando

Figura 25 – Exemplo de ensaio em curto-circuito  $V_{DS}=600V,\,T_{amb}=25\,\,^{\circ}C.$

a instabilidade da tensão limiar.

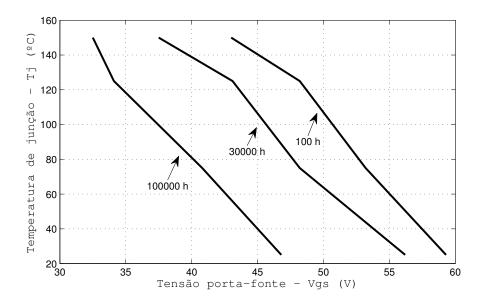

### 5.3 Previsão da vida útil do MOSFET SiC em função de $V_{GS}$

Há outro fator importante que deve ser estudado: a vida útil do componente. Deve-se conhecer o tempo necessário para que o componente se destrua, sendo o mesmo submetido a vários ensaios repetitivos. Para isso, será analisada a TDDB (*Time Dependent Dielectric Breakdown*). Esta, mostra o tempo de ruptura em função da tensão porta-fonte do MOSFET acoplado.

Figura 26 – Previsão do tempo de vida útil para o MOSFET SiC.

Os testes foram feitos no Laboratório Ampère e mostraram que o MOSFET SiC

pode permanecer funcionando por 642 horas e 50 minutos sob uma tensão  $V_{GS} = 40V$ . A partir da fusão destas duas curvas, pode-se traçar a TDDB(h) para as temperaturas de junção  $T_j = 25 \, ^{\circ}C$ , 75  $^{\circ}C$ , 125  $^{\circ}C$ , 150  $^{\circ}C$ . A exploração destas curvas permite determinar 3 tempos de vida útil dados a temperatura de junção em função da tensão porta-fonte, Fig. 26. [5] [22]

Pode-se, portanto, prever a qual temperatura de junção e tensão de porta-fonte não é permitido ultrapassar, caso deseja-se que o componente dure um certo tempo T. O gráfico mostra, também, que o tempo de vida útil do componente diminui quando se aumenta a temperatura de junção, o que é intuitivo imaginar, pois há maior possibilidade de degradação por efeito térmico. Por outro lado, a tensão  $V_{GS}$  máxima tende a diminuir com o aumento da temperatura de junção, do contrário, haverá uma condição de incontrolabilidade do MOSFET de potência.

## 6 Conclusão

Este trabalho tratou da robustez do MOSFET de carbeto de silício. Os ensaios foram realizados em avalanche e curto-circuito para estudar os limites físicos do componente.

A primeira parte abordou a área de operação segura dos MOSFETs SiC, detalhando as vantagens do carbeto de silício e os conceitos teóricos necessários para a compreensão do tema. Um método de traçado para a SOA foi realizado, analisando a influência do tipo de dissipador térmico sobre as performances do MOSFET SiC. Tanto o método inicial, quanto o modelo não-linear comentado, ofereceram resultados claros e precisos.

Seguindo o trabalho, a robustez do componente foi analisada. Esta característica é ligada à degração da camada de óxido da porta do transistor. Apresentou-se também um método de previsão do tempo de vida útil para o componente em função da tensão porta-fonte. Este ponto é fundamental, pois pode-se antever as condições de operação que serão submetidos os MOSFETs de potência.

Atualmente, a robustez da camada de óxido e a robustez em curto-circuito são estudadas em detalhe pelo Laboratório Ampère em Lyon, França. Um outro tema bastante discutido é o diodo interno associado ao MOSFET, pois o mesmo é considerado como estrutura fundamental na atuação de inversores sem diodos antiparalelos.

# Referências

- 1 MOUSA, R. Caractérisation, modélisation et intégration de JFET de puissance en carbure de silicium dans des convertisseurs haute température et haute tension. Tese (Doutorado) INSA de Lyon, 2009. Citado 2 vezes nas páginas 1 e 2.

- 2 HAMIEH, Y. Caractérisation et modélisation du transistor JFET en SiC à haute température. Tese (Doutorado) INSA de lyon, 2011. Citado 2 vezes nas páginas 1 e 2.

- 3 SCHOISWOH, J. Linear mode operation and safe operating diagram of power-mosfets. *Infineon Application Note*, 2010. Citado 3 vezes nas páginas 1, 10 e 22.

- 4 SADIK, D.-P. et al. Short-circuit protection circuits for silicon-carbide power transistors. *IEEE Transactions on Industrial Electronics*, IEEE, v. 63, n. 4, p. 1995–2004, 2016. Citado na página 1.

- 5 KIMURA, M. Field and temperature acceleration model for time-dependent dielectric breakdown. *IEEE Transactions on Electron Devices*, IEEE, v. 46, n. 1, p. 220–229, 1999. Citado 2 vezes nas páginas 1 e 30.

- 6 AMMOUS, A. et al. Choosing a thermal model for electrothermal simulation of power semiconductor devices. *IEEE Transactions on Power Electronics*, IEEE, v. 14, n. 2, p. 300–307, 1999. Citado 3 vezes nas páginas 1, 11 e 17.

- 7 HALL, R. N. Silicon carbide semiconductor devices and method of preparation thereof. [S.l.]: Google Patents, 1959. US Patent 2,918,396. Citado na página 2.

- 8 CREE, I. C. Cree.com, part no: C2m0080120d, silicon carbide power mosfet zfettm mosfet. *Datasheet Industrial*, n. 9. Citado 4 vezes nas páginas 4, 8, 10 e 16.

- 9 LOCHER, R. Introduction to power mosfets and their applications. *Fairchild Semiconductor, Application Note*, v. 558, 1998. Citado na página 4.

- 10 BARKHORDARIAN, V. et al. Power mosfet basics. *Powerconversion and Intelligent Motion-English Edition*, Ventura, Calif.: Intertec Communications, c1985-c1998., v. 22, n. 6, 1996. Citado 2 vezes nas páginas 4 e 10.

- 11 SEMICONDUCTOR, F.; SEMICONDUCTOR, F. Practical considerations of trench mosfet stability when operating in linear mode. *Application Note AN-4161*, 2013. Citado 2 vezes nas páginas 9 e 10.

- 12 BROWN, J. Power mosfet basics: Understanding gate charge and using it to assess switching performance. *Vishay Siliconix, AN608*, 2004. Citado na página 10.

- 13 MCDONALD, T. et al. Power mosfet avalanche design guidelines. *International rectifier Application Note, AN-1005*, 2000. Citado 3 vezes nas páginas 10, 12 e 15.

- 14 OETTINGER, F. F.; BLACKBURN, D. L.; RUBIN, S. Thermal characterization of power transistors. *IEEE Transactions on electron devices*, IEEE, v. 23, n. 8, p. 831–838, 1976. Citado na página 11.

Referências 33

15 DARWISH, A. M.; BAYBA, A. J.; HUNG, H. A. Thermal resistance calculation of algan-gan devices. *IEEE transactions on microwave theory and techniques*, IEEE, v. 52, n. 11, p. 2611–2620, 2004. Citado 2 vezes nas páginas 14 e 16.

- 16 GRAOVAC, D.; PURSCHEL, M.; KIEP, A. Mosfet power losses calculation using the data-sheet parameters. *Infineon application note*, v. 1, 2006. Citado na página 16.

- 17 GARRAB, H. Contribution à la modélisation électro-thermique de la cellule de commutation MOSFET-Diode. Tese (Doutorado) INSA de Lyon (France, 2003. Citado na página 25.

- 18 CHEN, C. et al. Robustness in short-circuit mode of sic mosfets. In: VDE. *PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of.* [S.l.], 2015. p. 1–8. Citado na página 27.

- 19 OTHMAN, D. Etude de la robustesse de transistors mosfet sic pour des applications aéronautiques. In: *Journées JCGE'2014-SEEDS*. [S.l.: s.n.], 2014. Citado 2 vezes nas páginas 27 e 28.

- 20 OUAIDA, R. et al. Etude sur les transistors mosfets en carbure de silicium-potentiel d'utilisation dans les applications hautes températures. In: *Symposium de Génie Électrique 2014.* [S.l.: s.n.], 2014. Citado na página 28.

- 21 LELIS, A. J.; GREEN, R.; HABERSAT, D. B. High-temperature reliability of sic power mosfets. In: TRANS TECH PUBL. *Materials Science Forum*. [S.l.], 2011. v. 679, p. 599–602. Citado na página 28.

- 22 ALVINO-SALVADO, O. Field and temperature acceleration model for time-dependent dielectric breakdown. *IEEE Transactions on Electron Devices*, Mémoire doctorant 1ère année, 2016. Citado na página 30.

# APÊNDICE A – Resistência Térmica junção-encapsulamento e encapsulamento-ambiente

A transferência térmica entre a junção e o módulo se faz essencialmente por condução. Condiderando uma parede espeça e com condutividade  $\lambda$  e de superfície S, a resistência térmica é dada pela equação (A.1).

$$R_c = \frac{e}{\lambda \cdot S}, \quad \text{com } \lambda(SiC, 20 \, ^{\circ}C) \approx [150 - 200]W \cdot m^{-1}K^{-1}$$

(A.1)

A transferência térmica encapsulamento-ambiente se faz por convecção, também. Considerando uma parece a uma temperatura  $T_c$ , superfície S sobre a qual circula um fluido, a resistência  $R_{cv}$  é dada pela equação (A.2).

$$R_{cv} = \frac{1}{h \cdot S}, \quad \text{com h em } W \cdot m^{-1} K^{-1}$$

(A.2)

A resistência térmica de convecção depende, sobretudo, da potência trocada que atravessa a superfície de contato.