## Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Programa de Pós-graduação em Engenharia Elétrica

## Circuito Integrado para Multiplicação em GF(2<sup>4</sup>) Utilizando Portas de Limiar Linear

Dissertação de mestrado submetida à Coordenação do Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande, em cumprimento às exigências para obtenção do grau de Mestre em Ciências no Domínio da Engenharia Elétrica.

#### Mestrando:

Cristóvão Mácio de Oliveira Lima Filho

#### Orientadores:

Prof. Dr. Raimundo Carlos Silvério Freire (UFCG)

Prof. Dr. Francisco Marcos de Assis (UFCG)

Campina Grande, maio de 2010

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA CENTRAL DA UFCG

L732c

Cristovão Mácio de Oliveira Lima Filho.

Circuito integrado para multiplicação em GF (2<sup>4</sup>) utilizando portas de limiar linear/Cristovão Mácio de Oliveira Lima Filho. — Campina Grande, 2010.

70 f.: il.

Dissertação (Mestrado em Engenharia Elétrica) – Universidade Federal de Campina Grande, Centro de Engenharia Elétrica e Informática.

Orientadores: Prof. Dr. Raimundo Carlos Silvério Freire e Prof. Dr. Francisco Marcos de Assis.

Referências.

1. Multiplicador de Mastrovito. 2. Redes Neurais Discretas. 3. Portas de Limiar Linear. I. Título.

CDU 004.315.5(043)

### CIRCUITO INTEGRADO PARA MULTIPLICAÇÃO EM GF(24) UTILIZANDO PORTAS DE LIMIAR LINEAR

#### CRISTÓVÃO MACIO DE OLIVEIRA LIMA FILHO

Dissertação Aprovada em 09.06.2010

RAIMUNDO CARLOS SILVÉRIO FREIRE, Dr., UFCG

Orientador

FRANCISCO MARCOS DE ASSIS, Dr., UFCG

Orientador/

Componente da Banca

Edmar Cartia G. EDMAR CANDEIA GURJÃO, D.Sc., UFCG

Componente da Banca

Componente da Banca

CAMPINA GRANDE - PB JUNHO - 2010

## Dedicatória

À minha mãe, Ana Lúcia, como gratidão por todo o esforço, dedicação e amor que tem para conosco.

À minha grande amiga, Ana Elizabeth, com quem compartilhei os melhores momentos da minha vida.

## Agradecimentos

Aos meus orientadores Raimundo Carlos Silvério Freire e Francisco Marcos de Assis, pela orientação e incentivo durante todo o desenvolvimento do trabalho.

Aos amigos da pós-graduação Alan, Bob, Carol, Eline, Euler, Georgina, Ilton, Karolie, Sabiniano, Selma e Thiago pela amizade e companheirismo e aos demais colegas que ao longo desses anos contribuíram para minha formação profissional e pessoal.

#### Resumo

Esta dissertação descreve o desenvolvimento de um leiaute de uma nova arquitetura de multiplicador em corpos finitos baseada no multiplicador de Mastrovito. Tal arquitetura tem como unidades de processamento as portas de limiar linear, que é o elemento básico de uma rede neural discreta.

As redes neurais discretas implementadas com portas de limiar linear permitem reduzir a complexidade de certos circuitos antes implementados com lógica tradicional (Portas AND, OR e NOT). Com isso, a idéia de estender o uso de portas de limiar linear em operações aritméticas em corpos finitos se torna bastante atraente. Assim, para comprovar de forma prática, a eficiência das portas de limiar linear, a arquitetura de um multiplicador em GF(2<sup>4</sup>), proposta em (LIDIANO - 2000), foi implementada utilizando as ferramentas de desenho de leiaute de circuito integrado da *Mentor Graphics*<sup>®</sup>.

Os resultados da simulação do leiaute do circuito integrado do multiplicador em  $GF(2^4)$  são apresentados. Os mesmos indicaram um desempenho abaixo do esperado, devido a complexidade espacial do multiplicador em  $GF(2^n)$  com n = 4 não ser suficiente para que as vantagens da implementação com portas de limitar linear sejam visualizada.

Palavras-chave: Multiplicador de Mastrovito, Redes Neurais Discretas, Portas de Limiar Linear.

**Abstract**

This dissertation describes the development of a layout of new multiplication

architecture in Galois field based on the Mastrovito multiplier. The processing unit of

this new architecture is a threshold logic gate, which is a basic element of a discrete

neural network.

The discrete neural network built with threshold logic gates allow reduce de complexity

of a certain circuits once built using traditional boolean gates (AND, OR and NOT).

Therewith, the idea of extending the advantages of the threshold logic gates for

arithmetic operations in Galois field to become very attractive. Thus, to confirm into

practice form, the advantages of the threshold logic gates, a multiplier architecture in

GF(2<sup>4</sup>), proposed in (LIDIANO - 2000), was implemented using the integrated circuit

layout tools of *Mentor Graphics*<sup>®</sup>.

The results from simulations of the layout of multiplier in GF(2<sup>4</sup>) are presented. These

results indicated a low performance, due to the space complexity of GF(2<sup>n</sup>) multiplier

with n = 4 is not enough for show the advantages of the multiplier implementation with

threshold logic gates.

Key Words: Mastrovito Multiplier, Discrete Neural Networks, Threshold Logic Gates.

iv

## Sumário

| 1. Introdução                                                   | 1  |

|-----------------------------------------------------------------|----|

| 1.1. Motivação                                                  | 1  |

| 1.2. Objetivo da Dissertação                                    | 3  |

| 1.3. Organização do Trabalho                                    | 4  |

| 2. Aritmética de GF(2 <sup>m</sup> ) em <i>Hardware</i>         | 5  |

| 2.1. Álgebra dos Corpos Finitos.                                | 5  |

| 2.1.1. Aritmética Modular                                       | 6  |

| 2.1.2. Grupos                                                   | 6  |

| 2.1.3. Anéis                                                    | 7  |

| 2.1.4. Corpos                                                   | 8  |

| 2.1.5. Polinômios Sobre Corpos Finitos                          | 9  |

| 2.1.6. Aritmética Modular com Polinômios                        | 9  |

| 2.1.7. Construção de Corpos com <i>p</i> <sup>m</sup> Elementos | 10 |

| 2.1.8. Bases de Corpos Finitos                                  | 11 |

| 2.2. Multiplicação em GF(2 <sup>m</sup> )                       | 12 |

| 2.2.1. Considerações Prévias                                    | 12 |

| 2.2.2. Multiplicador de Mastrovito                              | 13 |

| 2.2.3. Considerações Finais                                     | 15 |

| 3. Redes Neurais Discretas                                      | 16 |

| 3.1.Introdução                                                  | 16 |

| 3.2. Portas de Limiar Linear                                    | 16 |

| 3.2.1. Comportamento das Portas de Limiar                       | 17 |

| 3.3. Funções Simétricas.                                        | 18 |

| 3.4. Construção de Circuitos de Retardo Fixo                    | 19 |

| 3.4.1. Circuitos de Duas Camadas                                | 21 |

| 3.4.2. Circuitos de Três Camadas                                | 26 |

| 3.5. Implementação de Operações Aritméticas                     | 29 |

| 3.5.1. Adição                                                   | 29 |

| 3.5.2. Multiplicação                                            | 31 |

| 2.6. Canalugão                                                  | 25 |

| 4. Implementação do Multiplicador $\mathrm{GF}(2^4)$ com Portas de Limiar Linear37 |    |  |

|------------------------------------------------------------------------------------|----|--|

| 4.1. Introdução                                                                    | 37 |  |

| 4.2. Multiplicador de Mastrovito com Portas AON                                    | 37 |  |

| 4.2.1. Multiplicação Polinomial Ordinária                                          | 37 |  |

| 4.2.2. Redução Módulo <i>p(x)</i>                                                  | 39 |  |

| 4.3. Multiplicador de Mastrovito com Portas de Limiar Linear                       | 42 |  |

| 4.3.1. Multiplicação Polinomial Ordinária                                          | 42 |  |

| 4.3.2. Redução Módulo <i>p(x)</i>                                                  | 45 |  |

| 4.4. Conclusão                                                                     | 49 |  |

| 5. Leiaute do Multiplicador                                                        | 50 |  |

| 5.1. Introdução                                                                    | 50 |  |

| 5.2. Implementação da Porta de Limiar Linear                                       | 50 |  |

| 5.3. Leiaute do Multiplicador de GF(2 <sup>4</sup> ) Utilizando TLG                | 55 |  |

| 5.4. Conclusões                                                                    | 59 |  |

| 6. Conclusões e Trabalhos Futuros                                                  | 61 |  |

| 6.1. Conclusões                                                                    | 61 |  |

| 6.2. Trabalhos Futuros                                                             | 61 |  |

| Apêndice A – Complexidade                                                          | 63 |  |

| A.1. Notações Assintóticas.                                                        | 63 |  |

| A.2. Fan-in/Fan-out.                                                               | 65 |  |

| A.3. Complexidade Espacial                                                         | 66 |  |

| A.4. Complexidade Temporal (Profundidade)                                          | 66 |  |

| Referências Bibliográficas                                                         | 67 |  |

# Índice de Figuras

| Figura 1.1 – Estrutura geral de um sistema de comunicação digital                     | 1    |

|---------------------------------------------------------------------------------------|------|

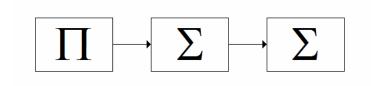

| Figura 2.1 – Diagrama de blocos do multiplicador de Mastrovito                        | 14   |

| Figura 3.1 – Modelo de uma porta de limiar                                            | 17   |

| Figura 3.2 – Portas de limiar que calculam funções booleanas: a) função AND e         | b)   |

| função OR                                                                             | 18   |

| Figura 3.3 – Solução para o problema do AND lógico utilizando uma porta de lir        | niar |

| linear                                                                                | 19   |

| Figura 3.4 – Modelo de uma Rede Neural com propagação direta                          | 20   |

| Figura 3.5 – Paridade de 4 variáveis com portas de limiar linear                      | 23   |

| Figura 3.6 – Paridade de 4 variáveis com circuito de 2 camadas, construído com a      | a    |

| técnica telescópica                                                                   | 25   |

| Figura 3.7 – Paridade de 4 variáveis com circuito de 3 camadas, construído com a      | a    |

| técnica telescópica                                                                   | 28   |

| Figura 3.8 – Bloco funcional do multiplicador                                         | 31   |

| Figura 3.9 – Exemplo de cálculo da soma múltipla usando a técnica <i>block-save</i>   | 34   |

| Figura 3.10 – Esquema de cálculo da soma múltipla usando a técnica block-save.        | 35   |

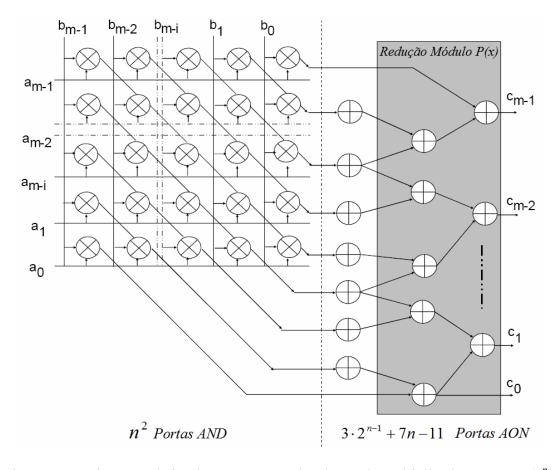

| Figura 4.1 – Diagrama da implementação em hardware de multiplicadores em              |      |

| GF(2 <sup>n</sup> )                                                                   | 41   |

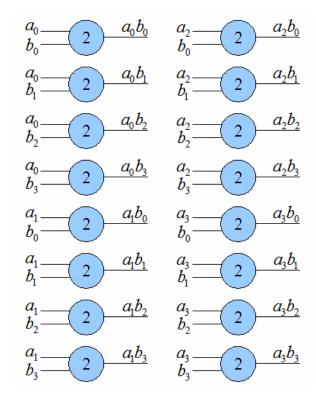

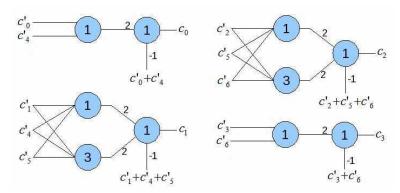

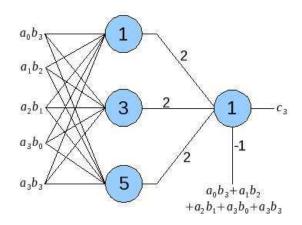

| Figura 4.2 – Primeira camada do multiplicador em GF(2 <sup>4</sup> )                  | 44   |

| Figura 4.3 – Implementação do cálculo dos bits $c_i$ 's utilizando portas de limiar   |      |

| linear                                                                                | 44   |

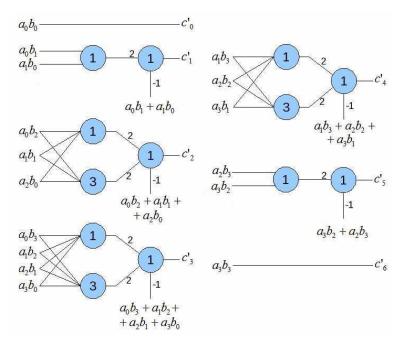

| Figura $4.4$ – Implementação do cálculo dos bits $c_i$ 's utilizando portas de limiar |      |

| linear                                                                                | 45   |

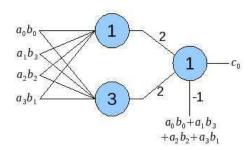

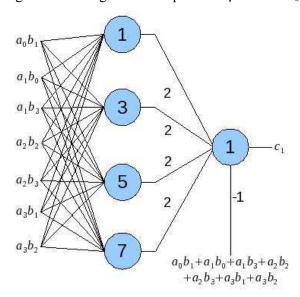

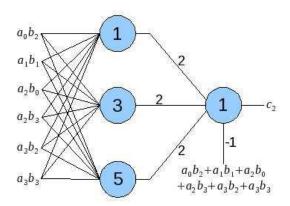

| Figura 4.5 – Diagrama da implementação do bit c <sub>0</sub>                          | 48   |

| Figura 4.6 – Diagrama da implementação do bit c <sub>1</sub>                          | 48   |

| Figura 4.7 – Diagrama da implementação do bit c <sub>2</sub>                          | 48   |

| Figura 4.8 – Diagrama da implementação do bit c <sub>3</sub>                          | 49   |

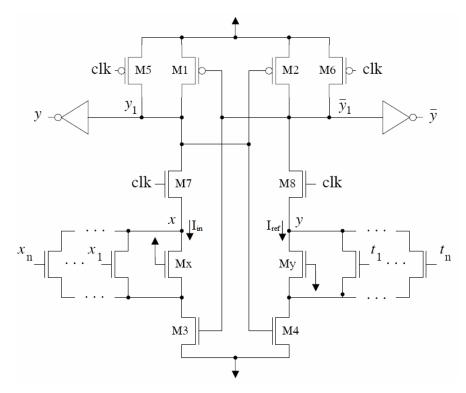

| Figura 5.1 – Esquema elétrico da porta de limiar baseada no comparador <i>latch</i>   | 51   |

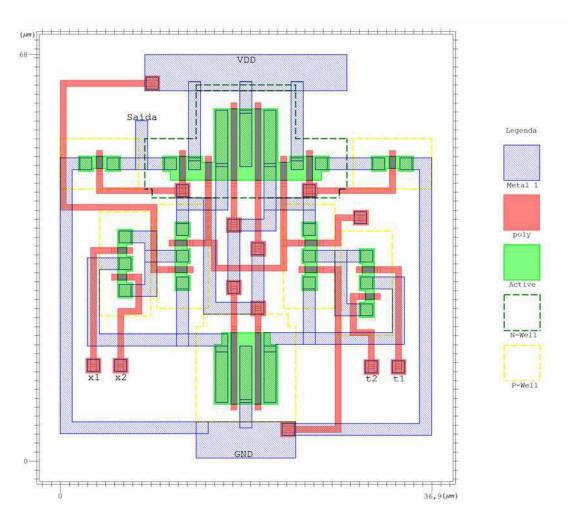

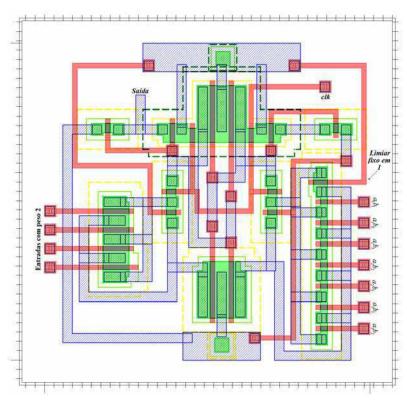

| Figura 5.2 – Leiaute da porta de limiar linear com duas entradas                      | 52   |

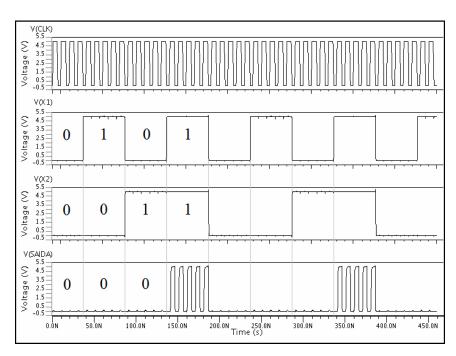

| Figura 5.3 – Simulação do leiaute da porta de limiar implementando uma função      |    |

|------------------------------------------------------------------------------------|----|

| AND                                                                                | 53 |

| Figura 5.4 – Simulação do leiaute da porta de limiar implementando uma função      |    |

| OR                                                                                 | 54 |

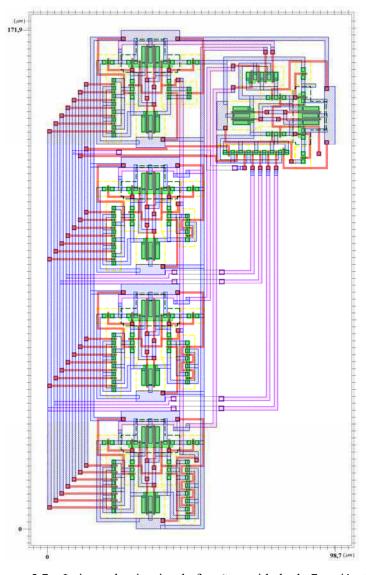

| Figura 5.5 – Leiaute da primeira camada do multiplicador em GF(2 <sup>4</sup> )    | 55 |

| Figura 5.6 – Leiaute da porta de limiar da segunda camada da função paridade de 7  | 7  |

| variáveis                                                                          | 56 |

| Figura 5.7 – Leiaute do circuito da função paridade de 7 variáveis                 | 57 |

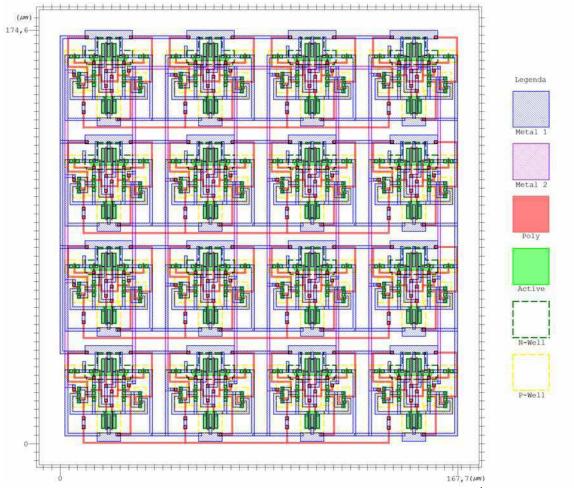

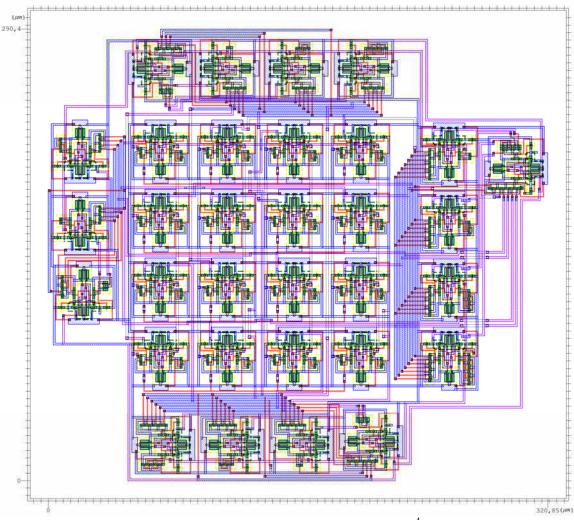

| Figura 5.8 – Leiaute do multiplicador em GF(2 <sup>4</sup> )                       | 58 |

|                                                                                    |    |

| Indice de Tabelas                                                                  | _  |

| Tabela 2.1 – Representação dos elementos de GF(2 <sup>4</sup> )                    |    |

| Tabela 3.1 – Soma de dois números de 2 bits                                        | 29 |

| Tabela 5.1 – Razão W/L dos transistores da porta de limiar linear implementada     | 53 |

| Tabela 5.2 – Resultados da simulação do leiaute da porta de limiar com duas        |    |

| entradas                                                                           | 54 |

| Tabela 5.3 – Resultados da simulação do leiaute da 1ª camada do multiplicador em   | :  |

| GF(2 <sup>4</sup> )                                                                | 55 |

| Tabela 5.4 – Resultados da simulação do leiaute da função paridade de 7 variáveis. | 58 |

| Tabela 5.5 – Resultados da simulação do multiplicador em GF(2 <sup>4</sup> )       | 58 |

| Tabela 5.6 – Comparação das arquiteturas de multiplicadores em GF(2 <sup>n</sup> ) | 60 |

## 1. Introdução

#### 1.1 – Motivação

Desde a publicação do artigo "A mathematical theory of communication" [1] por Claude Shannon, em 1948, a teoria da informação tem sido de grande importância para o desenvolvimento dos sistemas de comunicações digitais modernos e dos sistemas de armazenamento de dados. Nesses sistemas, dados são processados (recebidos, transmitidos ou armazenados) a velocidades elevadas e também em alguns desses sistemas está envolvida a transmissão de dados através de canais ruidosos, dessa forma há sempre a possibilidade de ocorrência de erros.

Resultados da teoria de Shannon garantem que é possível inserir redundâncias no sinal antes da transmissão ou armazenamento de modo que seja possível a detecção e/ou correção de erros. Essas redundâncias são incorporadas aos dados seguindo especificações definidas pelo código utilizado. Assim, o uso de códigos corretores de erros (*Error Correcting Codes* – ECC), tais como BCH (Bose, Chaudhuri e Hocquenghem), Goppa e RS (*Reed-Solomon Codes*) são uma constante nos meios de comunicação.

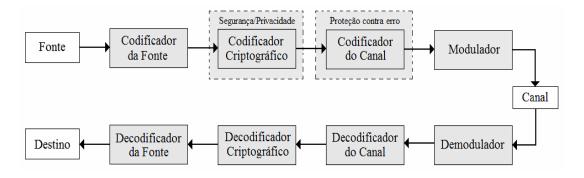

Na figura 1.1 é mostrada a estrutura de um sistema de comunicação digital simples. Nesse sistema, o dado digital proveniente da fonte é codificado, criptografado e modulado para a comunicação através do canal. O dado recebido é demodulado, descriptografado e decodificado para então ser utilizado. Todos os elementos desse sistema de comunicação são descritos matematicamente pelos teoremas da Teoria da Informação [2].

Figura 1.1 – Estrutura geral de um sistema de comunicação digital.

Como pode ser visto na figura 1.1, na transmissão de dados digitais há a possibilidade de ocorrência de erro nos dados, devido às interferências inseridas pelo canal, portanto, faz-se necessário a utilização de códigos corretores de erros, tais como BCH, Goppa e RS, para solucionar o problema mencionado. Uma outra questão é a garantia da transmissão segura da informação em canais públicos e privados, ou seja, sem o risco de que pessoas não autorizadas possam ler a informação transmitida. As técnicas para uma transmissão segura de informação são proporcionadas pela criptografía. Todas essas técnicas fazem uso da geometria algébrica como ferramenta para manipulação da informação.

A geometria algébrica, em particular os corpos finitos ou campos de Galois, tem se mostrado útil no desenvolvimento de soluções em diversas áreas da engenharia, como na codificação para controle de erros, em criptografía, em processamento digital de sinais, entre outras. Operações aritméticas em corpos finitos, tais como soma, multiplicação, divisão, cálculo de inversa e exponenciação, são de fundamental importância para as áreas mencionadas. Por exemplo, as operações de multiplicação e divisão são utilizadas nos codificadores e decodificadores em sistemas RS de correção de erros. Por sua vez, a soma, a multiplicação, o cálculo de inversa e exponenciação são fundamentais para o desenvolvimento de criptosistemas que operam com curvas elípticas.

Dentre as operações aritméticas em um corpo finito, a multiplicação é de grande importância, já que é a base de outras operações mais complexas, tais como divisão e exponenciação. Assim, são desejáveis multiplicadores em corpos finitos cada vez mais eficientes para a melhoria do desempenho dos sistemas que os utiliza em virtude da demanda por altas velocidades para esses sistemas.

Multiplicadores em corpos finitos podem ser implementados em *software* e em *hardware*. Implementações em *software* possuem a desvantagem da necessidade de grande quantidade de memória e capacidade de processamento [3]. Muitas pesquisas [4-11] têm sido desenvolvidas em busca de métodos de multiplicação em corpos finitos, implementados em *hardware*, cada vez mais rápidos e eficientes. A eficiência dessas arquiteturas depende fundamentalmente da forma de representação dos elementos do corpo [12]. Considerando um corpo finito com q elementos, representado por GF(q), em que os campos de interesse para aplicações em engenharia são os campos de extensão em GF(2) em razão da facilidade de mapeamento dos elementos do corpo em bits, já que os campos com extensão GF(2) são representados por 2 elementos (0 e 1) e são

designados por GF(2<sup>m</sup>). Existem distintas bases de representação dos elementos de GF(2<sup>m</sup>), sendo as mais populares a base canônica, a base normal e a base dual. Estas bases caracterizam os diferentes tipos de multiplicadores bem como sua complexidade.

Eficientes implementações em *hardware* têm sido realizadas em FPGA [13-17]. Muitas dessas implementações são realizadas utilizando portas AND, OR e NOT, chamadas de portas AON ou tradicionais. Uma possível solução para se obter arquiteturas de multiplicadores ainda mais eficientes é a utilização de portas com um potencial maior que as portas AON.

Arquiteturas que fazem uso de redes neurais têm se destacado em diversas aplicações [18-22], sobretudo no que diz respeito à complexidade computacional dos circuitos. O elemento básico de processamento dessas redes são portas que calculam uma função de limiar linear ou um elemento analógico que executa uma função sigmoidal. Essas portas de limiar vêm sendo estudadas desde 1960 e eficientes implementações em CMOS são descritas em [23-30]. Aplicações com portas de limiar lógicas [31,32] demonstram um grande potencial em obter altas velocidades de operação e redução de área do *chip*, se comparadas com a lógica convencional.

Este trabalho de dissertação descreve a implementação da arquitetura de um multiplicador em GF(2<sup>4</sup>) descrita em [33], no qual apresenta uma nova arquitetura para multiplicação em corpo finito utilizando portas de limiar linear, visando circuitos com complexidade reduzida.

Os resultados teóricos obtidos em [33] demonstraram que a utilização de portas de limiar linear em arquiteturas de multiplicação em corpos finitos é justificada, já que diminui consideravelmente a complexidade espacial e temporal do circuito do multiplicador se comparado com o mesmo multiplicador com portas tradicionais. Desta forma, torna-se necessário a implementação física da arquitetura proposta para comprovar sua viabilidade.

### 1.2 – Objetivo da Dissertação

O objetivo dessa dissertação de mestrado consiste no desenvolvimento de um circuito integrado que realize a multiplicação em GF(2<sup>4</sup>) utilizando portas de limiar linear como elemento de processamento. O multiplicador implementado é baseado na arquitetura de Mastrovito que apresenta uma das melhores medidas de complexidade

espacial se comparado com outras arquiteturas de multiplicadores em paralelo. Para tal objetivo, os seguintes passos são necessários:

- 1. Avaliar, de forma prática, o uso das portas de limiar linear em multiplicadores em corpos finitos, visando circuitos com menor complexidade espacial e temporal;

- 2. Escolher qual a melhor implementação, em CMOS, da porta de limiar linear para a utilização em multiplicadores em corpos finitos, tomando como parâmetros a potência dissipada, o atraso no cálculo da multiplicação e a área em *chip* ocupada;

- 3. Projetar o leiaute do circuito impresso do multiplicador em GF(2<sup>4</sup>) com as ferramentas de desenho de circuitos da *Mentor Graphics*.

#### 1.3 – Organização do Trabalho

Este trabalho está organizado da seguinte maneira: no capítulo 1 é feita uma breve introdução, onde é apresentada a motivação deste trabalho, bem como os passos necessários para realização do mesmo.

No capítulo 2 é realizada uma revisão da aritmética dos corpos finitos com uma abordagem na aplicação em Hardware.

No capítulo 3 são apresentadas as Redes Neurais Discretas. Algumas características e propriedades são levantadas, bem como conceitos relevantes para o desenvolvimento do trabalho. Neste capítulo é explicado como são construídos os circuitos que utilizam redes neurais discretas para o cálculo de operações de adição e multiplicação.

No capítulo 4 é apresentada a implementação de um multiplicador em GF(2<sup>4</sup>) construído com redes neurais discretas e baseado na arquitetura de Mastrovito.

No capítulo 5 são descritos os passos tomados para a construção do leiaute do multiplicador em  $GF(2^4)$  construído com portas de limiar linear. Neste capítulo, também são apresentados os resultados da simulação do leiaute do circuito do multiplicador.

No capítulo 6 são apresentadas as conclusões e sugestões para trabalhos futuros.

## 2. Aritmética de GF(2<sup>m</sup>) em *Hardware*

Neste capítulo são apresentados os fundamentos e as definições matemáticas para uma melhor compreensão do trabalho. Um estudo mais amplo a respeito da aritmética dos corpos finitos pode ser visto em [34-36].

No que diz respeito às implementações, a eficiência dos operadores em campos de Galois são caracterizadas pelas seguintes medidas:

- 1. **Complexidade espacial**: definida pelo número de portas lógicas requeridas para a construção do circuito;

- 2. **Complexidade temporal**: definida pelo número de retardos das portas ao longo da rota dos dados no circuito.

Uma arquitetura para unidades aritméticas em corpo finito pode ser serial ou paralela. Uma arquitetura paralela produz as saídas a partir de dados de entrada normalmente no período de um único ciclo de relógio. São circuitos tipicamente combinatórios, que favorecem o tempo de processamento em detrimento da complexidade espacial. Por outro lado, uma arquitetura serial utiliza em geral menos recursos materiais, em termos de portas lógicas, mas necessita de vários ciclos de relógio para produzir as saídas a partir das entradas. Como consequência, em uma arquitetura serial existem sempre elementos de memória, como *flip-flops* e registradores, o que implica na necessidade de um controle mais complexo em comparação com os circuitos paralelos.

Uma vez que o objetivo desta dissertação é produzir um multiplicador que responda às altas exigências em potência de cálculo, optou-se pela utilização exclusiva de arquiteturas paralelas para as unidades aritméticas em corpo finito.

## 2.1 – Álgebra dos Corpos Finitos

A aritmética dos Corpos Finitos é extensivamente usada em códigos corretores de erros, na geração de números Pseudo-aleatórios, em criptografia e em processamento digital de sinais. Um corpo finito, também chamado de campo de Galois, é um conjunto finito de elementos no qual são definidas algumas operações aritméticas. Nesta subseção são apresentadas definições algébricas básicas e propriedades dos corpos finitos, as quais são relevantes para o desenvolvimento deste trabalho.

#### 2.1.1 – Aritmética Modular

Dado um inteiro n, todo inteiro i pode ser unicamente expressado como i = qn + r para algum inteiro r, chamado de resto, no intervalo  $0 \le r \le n - 1$  e para algum inteiro q, chamado de quociente.

O resto r, denotado por  $r = i \mod n$ , em que " $\mod n$ " significa a operação em módulo n, é a parte mais importante da expressão, já que ele define a operação modular. O conjunto de possíveis restos  $\mod n$  é o conjunto de n inteiros  $R_n = \{0, 1, ..., n-1\}$ . É evidente que n é divisor de i se e somente se  $i \mod n = 0$ .

A aritmética que usa o conjunto de restos  $mod\ n$  é chamada de aritmética modular ou aritmética  $mod\ n$ . As leis da aritmética  $mod\ n$  seguem as mesmas leis da aritmética dos inteiros. Sendo  $r=i\ mod\ n$  e  $s=j\ mod\ n$ , ou seja, r=i-qn e s=j-tn, então:

$$r + s = i + j - (q + t)n;$$

(2.1)

$$rs = ij - (qj + ti)n + qtn^{2}.$$

(2.2)

Portanto,  $(r + s) \mod n = (i + j) \mod n$  e  $rs \mod n = ij \mod n$ , ou seja, o resto mod n da soma ou produto de dois inteiros é igual ao resto mod n da soma ou produto de dois restos mod n inteiros. Assim as leis da adição e da multiplicação mod n são definidas como:

$$r \oplus s = (r+s) \bmod n; \tag{2.3}$$

$$r * s = (rs) \bmod n. \tag{2.4}$$

em que no lado esquerdo da equação, r e s são elementos do conjunto de restos  $R_n$ , enquanto que no lado direito da equação, r e s correspondem a elementos do conjunto dos números inteiros.

#### 2.1.2 – Grupos

**Definição 2.1.** Um grupo é um conjunto de elementos  $G = \{a, b, c, ...\}$  e uma operação  $\circ$ , tal que as seguintes propriedades são satisfeitas:

1) Lei associativa: a operação é associativa, ou seja:

$$a \circ (b \circ c) = (a \circ b) \circ c \tag{2.5}$$

em que a, b e  $c \in G$ .

2) Identidade: existe um elemento identidade e em G, tal que:

$$a \circ e = e \circ a = a \tag{2.6}$$

para todo  $a \in G$ .

3) Inversa: para cada  $a \in G$ , existe um elemento  $a' \in G$ , tal que:

$$a' \circ a = a \circ a' = e \tag{2.7}$$

4) Condição de fechamento: para qualquer  $a \in G$  e  $b \in G$  , o elemento  $a \circ b$  é também um elemento de G .

Em todo grupo G o elemento identidade é único e ainda o inverso de cada elemento de G também é único. Portanto, dado um conjunto G e uma operação  $\circ$ , existem quatro propriedades que devem ser satisfeitas para que G seja um grupo: condição de fechamento, associatividade, existência de um elemento identidade e existência uma inversa para cada elemento de G.

Como exemplos de operações em um grupo, têm-se a adição e a multiplicação denotadas por  $\oplus$  e por \*, respectivamente. No caso da adição, o elemento identidade é o 0 e a inversa de a é -a. Já na multiplicação, o elemento identidade é o 1 e a inversa de a é  $a^{-1}$ . Um grupo G é dito ser comutativo ou abeliano quando  $a \circ b = b \circ a$ , para todo  $a,b \in G$ . Portanto, a notação de adição é geralmente usada para grupos comutativos e a notação de multiplicação é usada para grupos comutativos e não comutativos.

Um exemplo de grupo é o conjunto dos  $\Re$  com a operação de adição, em que o elemento identidade é 0 e a inversa de a é -a. O conjunto dos  $\Re$  menos o 0, denotado por  $\Re^*$  forma um grupo com a operação de multiplicação, em que o elemento identidade é o 1 e a inversa de a é  $a^{-1} = 1/a$ .

#### 2.1.3 - Anéis

**Definição 2.2.** Um anel, representado por  $(R, \oplus, *)$ , consiste em um conjunto R com duas operações  $\oplus$  e \* sobre R, tal que as seguintes propriedades são satisfeitas:

- 1)  $(R, \oplus)$  forma um grupo comutativo com o elemento identidade sendo 0;

- 2) (R, \*) forma um semigrupo, com a operação \* sendo associativa: a\*(b\*c) = (a\*b)\*c para todo  $a, b, c \in R$ ;

- 3) Existe uma unidade multiplicativa, denotada por 1, tal que: l\*a = a\*1, para todo  $a \in R$  e 1  $\neq$  0;

- 4) As operações estão relacionadas pela lei distributiva:  $(a \oplus b) * c = (a * c) \oplus (b * c)$ , para todo  $a, b, c \in R$ .

**Definição 2.3.** Se R é um anel arbitrário e existe um inteiro estritamente positivo n tal que nr = 0 para qualquer  $r \in R$ , então n é chamado de característica do anel R. Se tal inteiro positivo não existe, se diz que R possui característica 0.

**Definição 2.4.** Um elemento a de um anel R é chamado de elemento inversível se existe um elemento  $b \in R$  tal que a \* b = 1.

### 2.1.4 - Corpos

**Definição 2.5.** Um corpo é um conjunto F com pelo menos dois elementos e com duas operações  $\oplus$  e \*, para os quais as seguintes propriedades são satisfeitas:

- 1) O conjunto F forma um grupo comutativo sobre a operação  $\oplus$ ;

- 2) O conjunto  $F^* = F \{0\} = \{a \in F, a \neq 0\}$  forma um grupo comutativo sobre a operação  $\oplus$ ;

- 3) Lei distributiva: Para todo  $a, b, c \in F$ ,  $(a \oplus b) * c = (a * c) \oplus (b * c)$ .

Um corpo é um anel comutativo, no qual todos os elementos não nulos possuem inversos multiplicativos.

**Definição 2.6**. Um corpo finito é um conjunto F que contém um número finito de elementos. A ordem de F é seu número de elementos.

**Teorema 2.1.** Existência e Unicidade dos Corpos Finitos:

- 1) Se F é um corpo finito, então F contém  $q = p^m$  elementos para algum número primo p e um inteiro  $n \ge 1$ ;

- 2) Para todo número q da forma  $p^m$ , em que p é primo e  $m \ge 1$ , existe um único campo finito de ordem  $p^m$ . Este campo é denotado por  $F_q$  ou por GF(q).

**Teorema 2.2.** Subcorpo de um Corpo Finito: Seja  $F_q$  um campo finito de ordem  $q = p^m$ , então todo subcorpo de  $F_q$  tem ordem  $p^n$ , para algum  $n \le m$  que seja divisor de m.

#### 2.1.5 – Polinômios Sobre Corpos Finitos

Um polinômio f(x) não-nulo de grau m sobre um corpo F é expresso da seguinte forma:

$$f(x) = f_0 + f_1 x + f_2 x^2 + \dots + f_m x^m, \tag{2.8}$$

em que  $f_i \in F$ ,  $0 \le i \le m$ , e  $f_m \ne 0$ . O grau de f(x), denotado por deg(f(x)), é m. O símbolo x é uma incógnita. O conjunto de todos os polinômios sobre F é denotado por F[x] e forma um anel de polinômios.

**Definição 2.7.** Se R é um anel comutativo, o anel de polinômios R[x] é formado pelos polinômios com variável x e com coeficientes em R.

**Definição 2.8**. Seja  $f(x) = \sum_{i=0}^{m} a_i x^i$  um polinômio não nulo sobre R, então  $a_m \neq 0$ . O elemento  $a_m$  é chamado de coeficiente principal de f(x). Se o coeficiente principal de f(x) é 1, então f(x) é chamado de polinômio mônico.

**Definição 2.9.** Seja  $f(x) \in F[x]$ , assim f(x) é chamado de polinômio irredutível sobre F se este não pode ser representado como produto de dois polinômios em F[x].

#### 2.1.6 – Aritmética Modular com Polinômios

Dado um polinômio mônico g(x) de grau m, todo polinômio f(x) pode ser expresso como f(x) = q(x)g(x) + r(x) em que  $deg\ r(x) < m$ . Assim, o resto polinomial r(x) é denotado por  $r(x) = f(x) \ mod\ g(x)$ . O conjunto de todas as possibilidades de restos polinomiais é designado por  $R_{f,m} = \{r_0 + r_1x + \dots + r_{m-1}x^{m-1} \mid r_j \in F, 0 \le j \le m-1\}$ .

As leis da aritmética  $mod\ g(x)$  seguem as mesmas leis da aritmética polinomial. Sendo  $r(x) = f(x)\ mod\ g(x)$  e  $s(x) = h(x)\ mod\ g(x)$ , ou seja, r(x) = f(x) - q(x)g(x) e s(x) = h(x) - t(x)g(x), então:

$$f(x) + h(x) = r(x) + s(x) - (q(x) + t(x))g(x);$$

(2.9)

$$f(x)h(x) = r(x)s(x) - (q(x)s(x) + t(x)r(x))g(x) + q(x)t(x)g^{2}(x).$$

(2.10)

Portanto,  $(f(x) + h(x)) \mod g(x) = (r(x) + s(x)) \mod g(x)$  e  $f(x)h(x) \mod g(x) = r(x)s(x)$   $\mod g(x)$ . Assim as leis da adição e multiplicação polinomiais em  $\mod g(x)$  são definidas por:

$$r(x) \oplus s(x) = (r(x) + s(x)) \bmod g(x); \tag{2.11}$$

$$r(x) * s(x) = (r(x)s(x)) \mod g(x).$$

(2.12)

em que o lado esquerdo da equação, r(x) e s(x) são elementos do conjunto de restos polinomiais  $R_{F,m}$ , enquanto que no lado direito da equação, r(x) e s(x) correspondem a polinômios ordinários.

#### 2.1.7 – Construção de Corpos com $p^n$ Elementos

Uma representação muito utilizada para os elementos de um corpo finito  $F_q$ , com  $q = p^n$  e p sendo um número primo, é mediante uma base polinomial. Nesta base, os elementos de um corpo finito  $F_q$  serão representados por polinômios em  $Z_p[x]$  de grau < n, e com coeficientes em  $Z_p$ .

**Exemplo 2.1.** O campo finito  $F_{16}$ , em que  $16 = 2^4$ , pode ser representado pelo conjunto de polinômios sobre  $F_2$  de grau < 4. Ou seja,

$$F_{16} = \{a_3 x^3 + a_2 x^2 + a_1 x + a_0 \mid a_i \in \{0,1\}\}.$$

(2.13)

Por conveniência, cada polinômio  $a_3x^3 + a_2x^2 + a_1x + a_0$  é representado pelo correspondente vetor de coeficientes  $(a_3, a_2, a_1, a_0)$  de dimensão 4, assim:

$$F_{16} = \{(a_3, a_2, a_1, a_0) \mid a_i \in \{0,1\}\}. \tag{2.14}$$

Este tipo de representação é muito adequado para propósitos computacionais, já que o polinômio  $f(x) = x^4 + x + 1$  é irredutível sobre  $Z_2$ . As operações no corpo são realizadas em módulo f(x).

**Definição 2.10.** Um polinômio irredutível  $f(x) \in Z_p[x]$  de grau n é chamado de polinômio primitivo se x é um gerador de  $F_{p^n}^*$ .

**Exemplo 2.2.** Mediante o polinômio irredutível  $f(x) = x^4 + x + 1$ , se tem o polinômio p(x) = x como sendo um polinômio primitivo, e se diz que o elemento  $\alpha = (0, 0, 1, 0)$  do campo é um gerador de  $F_{2^4}^*$ . Dessa forma, tem-se:

$$F_{2^4}^* = \{ x^i \bmod f(x) \mid 0 \ge i < 2^4 - 1 \}.$$

(2.15)

#### 2.1.8 – Bases de Corpos Finitos

Um conjunto de n elementos linearmente independentes  $x = \{x_0, x_1, x_2, ..., x_{n-1}\}$  em  $GF(2^n)$  é chamado de base de  $GF(2^n)$  se um elemento  $x \in GF(2^n)$  for representado unicamente como uma soma ponderada dessa base sobre GF(2).

$$x = a_0 x_0 + a_1 x_1 + \dots + a_{n-1} x_{n-1}, \tag{2.16}$$

em que  $a_0$ ,  $a_1$ , ...,  $a_{n-1} \in GF(2)$ .

Existem diferentes tipos de bases para representar os elementos de um corpo finito. As três bases mais utilizadas para projetar operadores aritméticos sobre corpos finitos são: a base polinomial, a base normal e a base dual. Neste trabalho será utilizada apenas a base polinomial, já que o multiplicador desenvolvido é baseado na arquitetura de Mastrovito que é um multiplicador em GF(2<sup>n</sup>) com base polinomial.

#### **Base Polinomial**

Seja p(x) um polinômio irredutível sobre GF(2). Tomando  $\alpha$  como raiz de p(x), então  $A = \{1, \alpha, ..., \alpha^{n-1}\}$  é uma base polinomial de GF(2<sup>n</sup>).

**Exemplo 2.3.** Considerando GF( $2^4$ ) e o polinômio irredutível em GF(2) sendo  $p(x) = x^4 + x + 1$ . Tomando  $\alpha$  como raiz de p(x) então  $A = \{1, \alpha, \alpha^2, \alpha^3\}$  forma a base polinomial pois todos os 16 elementos podem ser representados como:

$$a = a_0 + a_1 \alpha + a_2 \alpha^2 + a_3 \alpha^3, \tag{2.17}$$

em que  $a_i \in GF(2)$ . Na tabela 2.1 são mostradas as diferentes formas de representação dos elementos de  $GF(2^4)$ .

A vantagem dos multiplicadores em base polinomial é que os mesmos não requerem conversão de base, tornando o projeto de multiplicadores em GF(2<sup>n</sup>) mais simples e mais eficiente se comparado, por exemplo, com o de multiplicadores de base dual.

| Elemento de GF(2 <sup>4</sup> ) | Representação Polinomial           | Representação Vetorial |

|---------------------------------|------------------------------------|------------------------|

| 0                               | 0                                  | (0, 0, 0, 0)           |

| α                               | α                                  | (0, 0, 1, 0)           |

| $\alpha^2$                      | $\alpha^2$                         | (0, 1, 0, 0)           |

| $\alpha^3$                      | $\alpha^3$                         | (1, 0, 0, 0)           |

| $\alpha^4$                      | $\alpha^3 + 1$                     | (1, 0, 0, 1)           |

| $\alpha^5$                      | $\alpha^3 + \alpha + 1$            | (1, 0, 1, 1)           |

| $\alpha^6$                      | $\alpha^3 + \alpha^2 + \alpha + 1$ | (1, 1, 1, 1)           |

| $\alpha^7$                      | $\alpha^2 + \alpha + 1$            | (0, 1, 1, 1)           |

| $\alpha^8$                      | $\alpha^3 + \alpha^2 + \alpha$     | (1, 1, 1, 0)           |

| $\alpha^9$                      | $\alpha^2 + 1$                     | (0, 1, 0, 1)           |

| $\alpha^{10}$                   | $\alpha^3 + \alpha$                | (1, 0, 1, 0)           |

| $\alpha^{11}$                   | $\alpha^3 + \alpha^2 + 1$          | (1, 1, 0, 1)           |

| $\alpha^{12}$                   | α+1                                | (0, 0, 1, 1)           |

| $\alpha^{13}$                   | $\alpha^2 + \alpha$                | (0, 1, 1, 0)           |

| $\alpha^{14}$                   | $\alpha^3 + \alpha^2$              | (1, 1, 0, 0)           |

| $\alpha^{15}$                   | 1                                  | (0, 0, 0, 1)           |

Tabela 2.1 – Representação dos elementos de GF(2<sup>4</sup>).

## 2.2 - Multiplicação em GF(2<sup>n</sup>)

### 2.2.1 – Considerações Prévias

Com base no que foi visto na seção anterior, têm-se as seguintes considerações:

Seja p um número primo. É sabido que o conjunto de restos módulo p,  $GF(p) = \{0, 1, ..., p-1\}$  é um corpo finito chamado primo. Todo corpo finito possui um elemento nulo e um elemento unidade e é uma extensão de grau finito de um corpo primo. Os corpos finitos ou campos de Galois são da forma  $GF(p^n)$ , em que p é primo, n é um inteiro positivo.  $GF(p^n)$  contém  $p^n$  elementos.

Em particular, para p=2,  $GF(2^n)$  contém  $2^n$  elementos e seu corpo primo é  $GF(2)=\{0,1\}$ . Seu grupo multiplicativo possui  $2^n-I$  elementos, no qual contém um

elemento  $\alpha$ , chamado de elemento primitivo, tal que todos os elementos de  $GF(2^n)$  –  $\{0\}$  podem ser representados como potências de tal elemento. Assim, tem-se:

$$GF(2^n) = \{0\} \cup \{\alpha^1, \alpha^2, \dots, \alpha^{2n-2}, \alpha^{2n-1} = 1\}.$$

(2.18)

Fazendo P( $\alpha$ ) = 0, tem-se:

$$\alpha^{n} = Q(\alpha) = q_{n-1}\alpha^{n-1} + q_{n-2}\alpha^{n-2} + \dots + q_{1}\alpha + q_{0}$$

(2.19)

A equação 2.19 é utilizada para representar qualquer elemento do corpo como um combinação linear única das potencias 1,  $\alpha$ ,  $\alpha^2$ , ...,  $\alpha^{n-1}$ . Portanto, qualquer elemento de  $GF(2^n)$  pode ser representado por uma forma polinomial em  $\alpha$  de grau n e coeficientes em GF(2). Em outras palavras, qualquer elemento  $A \in GF(2^n)$  pode ser representado da forma:

$$A(\alpha) = \sum_{i=0}^{n-1} a_i \alpha^i, \qquad (2.20)$$

em que  $a_i \in GF(2)$  para cada  $0 \le i \le n - 1$ . O conjunto  $\{1, \alpha, \alpha^2, ..., \alpha^{n-1}\}$  é dito ser a base polinomial.

Para implementar operações em *hardware*, a representação polinomial de cada elemento pode ser feita com um vetor binário com n elementos, da forma  $(a_{n-1}, a_{n-2}, ..., a_0)$ , esta representação é chamada de vetorial. Como p = 2, os elementos do campo podem ser representados convenientemente pelos dois sinais lógicos "0" e "1". Desta forma, a operação de adição módulo 2 é equivalente a uma operação XOR e a operação de multiplicação módulo 2 a uma operação AND.

### 2.2.2 – Multiplicador de Mastrovito

Em [8], Mastrovito desenvolve um multiplicador sobre GF(2<sup>n</sup>), paralelo de base polinomial. Sua arquitetura apresenta baixa complexidade temporal e espacial se comparada com a de outros multiplicadores de base polinomial [9]. Nessa subseção será mostrado como é realizada a multiplicação em GF(2<sup>n</sup>), baseada na arquitetura do multiplicador de Mastrovito.

Para o cálculo do produto de dois elementos arbitrários, considere A(x), B(x) e  $C(x) \in GF(2^n)$  com  $GF(2^n)$  escrito na forma polinomial; a multiplicação é realizada da seguinte forma:

$$C(x) = A(x) \cdot B(x) \bmod P(x)$$

$$= (a_{n-1}x^{n-1} + \dots + a_0) \cdot$$

$$(b_{n-1}x^{n-1} + \dots + b_0) \bmod P(x)$$

(2.21)

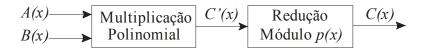

em que P(x) é o polinômio irredutível de grau n em GF(2). O multiplicador de Mastrovito realiza a multiplicação em duas etapas, como mostrado na figura 2.1.

Figura 2.1 – Diagrama de blocos do multiplicador de Mastrovito.

Na primeira etapa é efetuada a multiplicação polinomial, A(x)B(x), como mostrado na Equação (2.22).

$$C'(x) = A(x) \cdot B(x)$$

$$= (a_{n-1}x^{n-1} + \dots + a_0) \cdot (b_{n-1}x^{n-1} + \dots + b_0)$$

$$= a_0b_0 + (a_1b_0 + a_0b_1)x +$$

$$+ (a_2b_0 + a_1b_1 + a_0b_2)x^2 + \dots + (a_{n-1}b_{n-1})x^{2n-2}$$

(2.22)

Esta etapa requer  $n^2$  portas AND e  $n^2 - 2n + 1$  portas XOR [22].

Na segunda etapa é calculada a redução módulo P(x) para encontrar o resultado final  $C(x) \in GF(2^n)$ . Esta etapa depende do polinômio irredutível escolhido, que para este caso foi escolhido um trinômio da forma  $P(x) = x^n + x + 1$ . A expressão final para C(x) é mostrada na Equação (2.23):

$$C(x) = (c_0' + c_n') + (c_1' + c_n' + c_{n+1}')x + \dots + + (c_{n-2}' + c_{2n-2}' + c_{2n-3}')x^{n-2} + + (c_{n-1}' + c_{2n-2}')x^{n-1}$$

(2.23)

Para a redução em módulo P(x) são usadas 2n-2 portas XOR. O atraso total, considerando todas as portas, é dado por:

$$T \le \tau_{AND} + 2\tau_{XOR} \lceil \log_2 n \rceil \tag{2.24}$$

em que  $\tau_{AND}$  e  $\tau_{XOR}$  são os atrasos correspondentes às portas AND e XOR, respectivamente.

#### 2.2.3 – Considerações Finais

Como mencionado na introdução, as implementações em *hardware* de operadores aritméticos em corpos finitos GF(2<sup>n</sup>) são uma boa alternativa em relação às implementações em *software*, devido à maior segurança e desempenho obtidas as mesmas. Tais implementações em *hardware* podem ser feitas de duas formas: utilizando circuitos VLSI (*Very Large Scale Integration*) ou circuitos programáveis, como FPGA.

Dentre essas formas de implementação, optou-se pela utilização de circuitos VLSI, que cada vez mais se identificam com os ASIC (*Application Specific Integrated Circuit*) [35].

## 3. Redes Neurais Discretas

#### 3.1 – Introdução

A idéia do modelamento de neurônios em unidades discretas foi introduzida por McCulloch e Pitts [37] em 1943. Cada neurônio é modelado como um elemento de limiar linear com uma saída binária. Desde o início dos estudos de redes neurais, modelos discretos dessas redes tem sido parte integrante nas pesquisas em computação neural.

Indubitavelmente, tal modelo binário do neurônio não pode modelar toda a complexidade inerente ao sistema neural biológico. Entretanto, o interesse em um modelo binário reside em sua simplicidade. O modelo binário de McCulloch e Pitts não é usado somente em pesquisas na área de redes neurais, é usado, também, no desenvolvimento de computadores digitais. Recentes pesquisas em redes neurais demonstram um contínuo esforço no desenvolvimento de princípios computacionais baseados na neurobiologia. Nesse capítulo são introduzidos aspectos importantes das redes neurais discretas.

#### 3.2 – Portas de Limiar linear

A demanda por alto desempenho de processadores em escala de integração VLSI tem impulsionado as pesquisas por sistemas que garantam alto desempenho utilizando pouca área em *chip* e que apresentem baixo consumo de potência.

As portas lógicas de limiar (*Threshold Logic Gate* - TLG) vêm sendo estudadas desde 1960 e implementações eficientes em CMOS são descritas em [23-30]. Portas lógica de limiar podem calcular qualquer função linearmente separável, ou seja, funções cuja saída só depende do somatório de suas entradas ponderadas, e seu funcionamento básico é baseado na comparação entre a soma ponderada das entradas da porta e um certo limiar.

#### 3.2.1 – Comportamento das Portas de Limiar

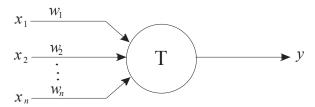

Uma porta de limiar linear é um elemento básico de uma rede neural que pode conter n entradas binárias, representadas por  $x_1$ ,  $x_2$ , ...,  $x_n$ , e apenas uma saída binária y, como pode ser visto na figura 3.1.

Figura 3.1 – Modelo de uma porta de limiar

A função booleana calculada por uma porta de limiar é chamada de função de limiar e é especificada pelo seu limiar T e seus pesos  $w_1$ ,  $w_2$ , ...,  $w_n$ , em que  $w_i$  é o peso correspondente a cada variável de entrada  $x_i$ . Uma porta de limiar linear pode calcular qualquer função booleana dada por:

$$f(X) = Y = \begin{cases} 1 & se \sum_{i=1}^{k} w_i \cdot x_i \ge t \\ 0 & se \sum_{i=1}^{k} w_i \cdot x_i < t \end{cases}$$

(3.1)

A função ainda pode ser escrita de uma forma mais compacta utilizando a notação *sgn*, dada por:

$$Y = \operatorname{sgn}\left(\sum_{i=1}^{n} w_i x_i - t\right),\tag{3.2}$$

em que  $x_i$  é a i-ésima entrada booleana,  $w_i$  é comumente referido como peso da i-ésima entrada e t é o limiar da função f(X). A função sgn é definida por  $sgn(\alpha)=1$  se  $\alpha \ge 0$ ,  $sgn(\alpha)=0$  caso contrário. Dessa forma, uma porta de limiar linear realiza a comparação entre o valor do somatório das entradas multiplicadas pelos seus respectivos pesos,  $\sum x_i w_i$ , e o valor do limiar t. Se o valor do somatório for maior ou igual ao limiar a saída da porta será o nível lógico 1, caso contrário, a saída será o nível lógico 0. Diferentes escolhas de w e t resultam em portas de limiar que calculam diferentes funções booleanas, por exemplo, na figura 3.2 são mostradas portas de limiar configuradas para calcular as funções booleanas AND e OR.

Figura 3.2 – Portas de limiar que calculam funções booleanas: a) função AND e b) função OR.

Essa versatilidade das portas de limiar linear oferece um avanço computacional significativo em comparação com as portas lógicas tradicionais, AND-OR-NOT [38], especialmente em aplicações que requerem um alto número de variáveis de entrada.

#### 3.3 – Funções Simétricas

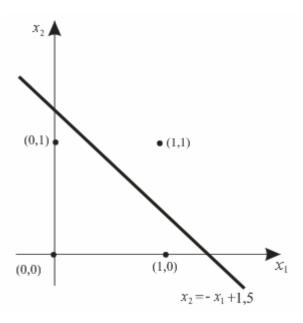

As portas de limiar linear estão restritas à soluções de problemas que sejam linearmente separáveis, ou seja, a problemas cuja solução pode ser obtida pela separação de duas regiões por meio de uma reta (ou um hiperplano para o caso n-dimensional). A equação de separação linear pode ser facilmente visualizada para o caso bidimensional. Considere como exemplo ilustrativo, um nó com duas entradas  $x_1$  e  $x_2$ , pesos  $w_1$  e  $w_2$ , limiar t e saída y executando uma função qualquer. A condição de disparo do nó (y=1) é então definida por  $x_1w_1 + x_2w_2 = t$ , que pode ser descrita na forma geral da equação de uma reta em que  $x_2=f(x_1)$ , conforme é mostrada na equação 3.3. Portanto, a superfície de decisões de uma porta de limiar linear está restrita a uma reta. Na figura 3.3 é mostrada a solução para o problema do AND lógico por meio de uma porta de limiar linear.

$$x_2 = -\left(\frac{w_1}{w_2}\right) x_1 + \left(\frac{t}{w_2}\right) \tag{3.3}$$

Figura 3.3 – Solução para o problema do AND lógico utilizando uma porta de limiar linear. Para este caso, tem-se  $w_1$ = $w_2$ =1 e t=1,5.

Para o caso particular em que  $x \in \{0, 1\}^n$ , que restringe as entradas a valores binários, tem-se que  $y : \{0, 1\}^n \to \{0, 1\}$  para  $w \in R^n$ . Apesar de estarem limitadas à resolução de problemas linearmente separáveis, que corresponde a uma pequena parcela do total de  $2^{2^n}$  funções booleanas possíveis com n entradas, as portas de limiar lineares são mais poderosas do que as portas lógicas convencionais. Com uma mesma porta de limiar linear pode-se implementar qualquer uma das funções AND, OR, NAND e NOR, entre outras, bastando mudar os parâmetros da porta.

### 3.4 – Construção de Circuitos de Retardo Fixo

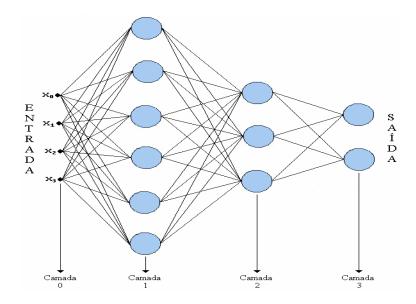

Como as portas de limiar linear estão restritas à solução de funções simétricas, o projeto de circuitos de limiar compreenderá, para este trabalho, a implementação de funções booleanas simétricas. O modelo de rede neural utilizada neste trabalho para a implementação dos circuitos é o de propagação direta, em que cada elemento em uma camada calcula uma função de limiar que de pende apenas dos valores das saídas da camada anterior, como pode ser visto na figura 3.4. Nessa seção serão apresentadas formas eficientes de construção de circuitos de limiar com duas e três camadas.

Figura 3.4 – Modelo de uma Rede Neural com propagação direta.

**Definição 3.1.** Uma função booleana f é simétrica se sua saída depende apenas do somatório dos seus valores de entrada.

Um exemplo de função simétrica é a função paridade, cuja saída é 1 se o somatório da entrada for ímpar e 0 caso contrário. Se a função depender apenas da soma ponderada das entradas, então a chamamos de função booleana generalizada.

**Teorema 3.1.** Toda função booleana  $f(x_1, x_2, ..., x_n) : \{0,1\}^n \to \{0,1\}$  pode ser computada por um circuito de limiar com duas camadas e no máximo  $2^{n-1} + 1$  portas de limiar linear.

**Prova:** Qualquer função booleana pode ser escrita como uma Soma de Produtos (SDP), da seguinte forma:

$$f(x_1, x_2, ..., x_n) = P_1 \vee P_2 \vee \cdots \vee P_k$$

(3.4)

em que cada termo  $P_i$  é um produto implementado por uma função AND de n variáveis e  $k \le 2^n$ . Alternativamente, f pode ser escrita como um Produto de Somas (PDS), da seguinte forma:

$$f(x_1, x_2, \dots, x_n) = S_1 \wedge S_2 \wedge \dots \wedge S_l$$

(3.5)

em que cada termo  $S_i$  é uma soma implementada pela função OR de n variáveis e  $l \leq 2^n$ .

Sendo  $2^n$  entradas distintas, segue que  $k+l=2^n$ , já que a SDP e a PDS formam subconjuntos de variáveis complementares, ou seja,  $2^n$  é o número máximo de produtos e somas com n variáveis booleanas. Dessa forma, a primeira camada do circuito de limiar implementará, para a SDP, os produtos  $P_i$  e a segunda camada é uma função OR que calculará f, utilizando assim  $2^{n-1}+1$  portas tradicionais. Como uma porta neural pode simular portas AND e OR, é possível implementar qualquer função booleana utilizando  $2^{n-1}+1$  portas neurais. Entretanto, essa construção requer o uso de circuitos cujo número de portas cresce exponencialmente com o aumento do número de entradas. Portanto, faz se necessário o estudo de técnicas, que fazem uso das redes neurais discretas, para a construção de circuitos de limiar que calculam certas classes de funções de maneira eficiente e que o número de portas de limiar aumenta polinomialmente com o aumento do número de entradas. Essas técnicas serão apresentadas a seguir.

#### 3.4.1 – Circuitos de duas camadas

Nessa subseção é apresentada uma técnica para construção de circuitos de limiar linear de 2 camadas que computa qualquer função booleana simétrica f com no máximo n+1 portas, em que n é o número de entradas do circuito.

Seja  $X = [x_1, x_2, ..., x_n]$  a entrada booleana do circuito e f uma função booleana simétrica. Como f depende apenas do somatório das entradas, existe um conjunto de valores em  $\sum_{k=1}^{n} x_k$  no qual a função f é 1. Agrupando esses valores em subintervalos de [0,n] tem-se s subintervalos dados a seguir:

$$[q_1, \widetilde{q}_1], [q_2, \widetilde{q}_2], ..., [q_s, \widetilde{q}_s]$$

(3.6)

em que  $q_k$  e  $\widetilde{q}_k$  são inteiros,  $q_{k+1} > \widetilde{q}_k + 1$  e  $q_k \le \widetilde{q}_k$  de tal forma que  $f(x_1, x_2, ..., x_n) = 1$ , se e somente se para algum j, tal que:

$$\sum_{k=1}^{n} x_k \in [q_j, \widetilde{q}_j] \tag{3.7}$$

Na primeira camada do circuito, são necessárias 2s portas de limiar linear calculando:

$$y_{q_j} = \operatorname{sgn}\left(\sum_{k=1}^n x_k - q_j\right) \tag{3.8}$$

e

$$\widetilde{y}_{q_j} = \operatorname{sgn}\left(\widetilde{q}_j - \sum_{k=1}^n x_k\right) \tag{3.9}$$

em que j = 1, 2, ..., s.

A segunda camada contém uma única porta neural que calcula:

$$f(x_1, x_2, ..., x_n) = \operatorname{sgn}\left(\sum_{k=1}^{s} (y_{k_j} + \widetilde{y}_{k_j}) - s - 1\right)$$

(3.10)

Para comprovar se o circuito fornece a resposta certa temos que, para j=1,2,...,s, se  $\sum_{k=1}^{n}x_{k}\notin [q_{j},\widetilde{q}_{j}]$ , então  $y_{k_{j}}+\widetilde{y}_{k_{j}}=1$  para todos os j. Assim:

$$\operatorname{sgn}\left(\sum_{k=1}^{s} (y_{k_j} + \widetilde{y}_{k_j}) - s - 1\right) = \operatorname{sgn}(s - s - 1) = 0$$

(3.11)

Caso  $\sum_{k=1}^{n} x_k \in [q_j, \widetilde{q}_j]$ , então  $y_{k_j} + \widetilde{y}_{k_j} = 2$  e  $y_{k_i} + \widetilde{y}_{k_i} = 1$  para  $i \neq j$ . Assim:

$$\operatorname{sgn}\left(\sum_{k=1}^{s} (y_{k_j} + \widetilde{y}_{k_j}) - s - 1\right) = \operatorname{sgn}(s + 1 - s - 1) = 1$$

(3.12)

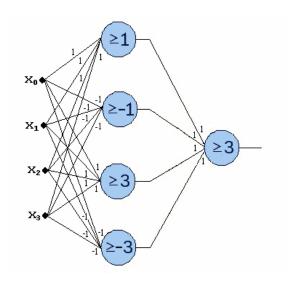

Portanto, a primeira camada possui apenas 2s portas. Como s é no máximo  $\left\lceil \frac{n}{2} \right\rceil$  e a segunda camada possui apenas uma porta, o número total de portas de limiar linear utilizadas é de n+1. Como cada porta no circuito possui *fan-in* de no máximo n, o número de conexões é  $O(n^2)$  (ver apêndice A). Para ilustrar o projeto de circuitos de limiar linear com 2 camadas, na figura 3.5 é mostrado o diagrama da implementação de uma função de paridade de 4 variáveis. Esse circuito necessita de 5 portas de limiar linear para implementar a paridade. Utilizando a lógica tradicional são necessárias 8 portas AND e 1 porta OR para implementar a mesma função. Para 10 variáveis de entrada são necessárias 512 portas AND e 1 porta OR, enquanto que se for utilizada a lógica neural, apenas 11 portas seriam necessárias.

Figura 3.5 – Paridade de 4 variáveis com portas de limiar linear.

É possível diminuir ainda mais o número de portas de limiar linear, para isso é necessário utilizar de uma técnica chamada de técnica telescópica, que será apresentada a seguir.

**Lema 1**. Seja o intervalo [0,n] dividido em s+1 subintervalos  $[b_0,b_1-1],[b_1,b_2-1],...,[b_{s-1},b_s-1],[b_s,n]$ , em que  $0=b_0 < b_1 < ... < b_k < n$ .

Seja

$$y_i = \operatorname{sgn}\left(\sum_{j=1}^n x_j - b_i\right)$$

, para todo  $i = 1, ..., k$ . Então:

$$\sum_{j=1}^{k} (a_j - a_{j-1}) y_j = a_m$$

(3.13)

Se  $\sum_{j=1}^n x_j \in [b_m, b_{m-1} - 1]$ , em que  $a_0 = 0$  e  $a_1, ..., a_k$  são números reais arbitrários.

**Prova:** Como  $y_i = \operatorname{sgn}\left(\sum_{j=1}^n x_j - b_i\right) = 1$  se e somente se  $\sum_{j=1}^n x_j \ge b_i$ , portanto, se  $\sum_{j=1}^n x_j \in [b_m, b_{m+1}]$  então  $y_1 = y_2 = \dots = y_m = 1$  e  $y_{m+1} = \dots = y_k = 0$ . Dessa forma, tem-

se:

$$\sum_{j=1}^{k} (a_j - a_{j-1}) y_j = \sum_{j=1}^{m} (a_j - a_{j-1}) = a_m$$

(3.14)

Note que  $\sum_{j=1}^n x_j \in [b_0,b_1-1]$ , ou seja m=0, então  $y_i=0$  para todo i=1,...,k e consequentemente  $\sum_{j=1}^k (a_j-a_{j-1})y_j=0=a_0$ .

Utilizando o lema 1, pode-se obter um circuito de limiar de duas camadas com no máximo  $\left\lceil \frac{n}{2} \right\rceil + 1$  portas que calculam funções simétricas.

Seja f(X) uma função simétrica de n variáveis. Seja um conjunto de inteiros,  $s_i$  e  $S_i$ , com  $0 \le s_i \le S_i \le n$  para  $i = 1, ..., \tau$  e  $S_i + 1 < s_{i+1}$  para  $i < \tau$ , tal que f(X) = 1 se e somente se para algum i com:

$$S_i \le \sum_{j=1}^n x_j \le S_i \tag{3.15}$$

A primeira camada do circuito consiste de  $\tau$  portas de limiar linear calculando  $y_i = \mathrm{sgn} \Bigg( \sum_{j=1}^n x_j - s_i \Bigg) \text{ para cada } i \text{ , sendo } 1 \leq i \leq \tau \text{ . A segunda camada possui uma única}$  porta que calcula a seguinte função:

$$z = \operatorname{sgn}\left(\sum_{j=1}^{n} (S_j - S_{j-1})y_j - \sum_{j=1}^{n} x_j\right)$$

(3.16)

em que é definido  $S_0 = -1$ .

Para verificar se o circuito fornece a resposta correta, note que para algum m,  $\sum_{i=1}^n x_j \in [s_m, s_{m+1} - 1]$ . Utilizando o lema 1, tem-se:

$$\sum_{j=1}^{\tau} (S_j - S_{j-1}) y_j = S_m$$

(3.17)

Se

$$f(X) = 1$$

, então  $s_m \le \sum_{j=1}^n x_j \le S_m$  e, portanto,  $z = \operatorname{sgn}\left(S_m - \sum_{j=1}^n x_j\right) = 1$ . Por

outro lado, se f(X) = 0, então  $S_m < \sum_{j=1}^n x_j \le s_{m+1} - 1$  e, portanto,

$$z = \operatorname{sgn}\left(S_m - \sum_{j=1}^n x_j\right) = 0.$$

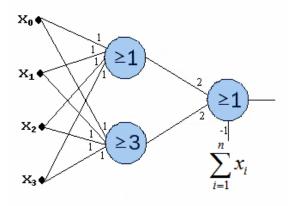

O número de portas de limiar linear no circuito é de  $\tau+1$ . Como  $\tau$  é no máximo  $\left\lceil \frac{n}{2} \right\rceil$ , então o número máximo de portas de limiar linear é de  $\left\lceil \frac{n}{2} \right\rceil+1$ . Na

figura 3.6 é mostrado um circuito que calcula a paridade de 4 variáveis utilizando apenas 3 portas de limiar linear, o que comprova a validade da técnica telescópica.

Figura 3.6 – Paridade de 4 variáveis com circuito de 2 camadas, construído com a técnica telescópica.

#### 3.4.2 – Circuitos de três camadas

Generalizando a técnica telescópica para construções de circuitos de 3 camadas, em que, neste caso, também é possível uma redução do número de portas de limiar linear. Como resultados, são obtidos circuitos que calculam funções simétricas com  $2\sqrt{n} + 1$  portas de limiar linear.

Novamente, utilizando um conjunto de inteiros  $s_i$  e  $S_i$ , em que  $i=1,...,\tau$ , com  $s_i \le S_i \le s_{i+1}$ , tal que f(X)=1 se e somente se:

$$S_i \le \sum_{j=1}^n x_j \le S_i \tag{3.18}$$

Dividindo o intervalo [0,n] em d subintervalos consecutivos  $[s_1,s_{2_1}-1],[s_2,s_{3_1}-1],...,[s_{d_1},n]$  tal que cada subintervalo, exceto possivelmente o último, contenha o mesmo número l de inteiros  $s_i$  e  $S_i$ , em que  $l \leq \left\lceil \frac{n}{2d} \right\rceil$ . O i-ésimo subintervalo conterá os inteiros  $s_{i_1} \leq S_{i_1} < s_{i_2} \leq S_{i_2} < ... < S_{i_1} \leq S_{i_1}$ .

A primeira camada do circuito consiste em d elementos de limiar linear, os quais calculam a seguinte função:

$$z_{i} = \operatorname{sgn}\left(\sum_{j=1}^{n} x_{j} - s_{i_{1}}\right)$$

(3.19)

para i = 1, ..., d.

Para cada k = 1, ..., l, são definidas duas somas telescópicas dadas por:

$$T_{k} = S_{1_{k}} z_{1} + (S_{2_{k}} - S_{1_{k}}) z_{2} + (S_{3_{k}} - S_{2_{k}}) z_{3} + \dots + (S_{d_{k}} - S_{d-1_{k}}) z_{d}$$

$$t_{k} = S_{1_{k}} z_{1} + (S_{2_{k}} - S_{1_{k}}) z_{2} + (S_{3_{k}} - S_{2_{k}}) z_{3} + \dots + (S_{d_{k}} - S_{d-1_{k}}) z_{d}$$

$$(3.20)$$

Observe que  $t_k$  e  $T_k$  são combinações lineares das saídas da primeira camada. A segunda camada consiste em 2l portas de limiar linear, cada uma utiliza os inteiros  $t_k$  ou  $T_k$  como valor de limiar para o cálculo de  $Q_k$  e  $q_k$  definidos a seguir:

$$Q_k = \operatorname{sgn}\left(T_k - \sum_{j=1}^n x_j\right)$$

$$q_k = \operatorname{sgn}\left(t_k - \sum_{j=1}^n x_j\right)$$

(3.21)

A terceira camada é uma única porta que calcula a seguinte função:

$$f(X) = \operatorname{sgn}\left(\sum_{k=1}^{l} 2(Q_k + q_k) - 2l - 1\right)$$

(3.22)

Para verificar se o circuito fornece a resposta correta, supomos que  $\sum_{j=1}^{n} x_j$  pertence ao m-ésimo intervalo em s, ou seja,  $\sum_{j=1}^{n} x_j \in [s_{m_1}, s_{(m-1)_1} - 1]$ . Utilizando o lema 1, a soma telescópica de  $T_k$  e  $t_k$  assume os seguintes valores:

$$T_k = S_{m_k}$$

$$t_k = S_{m_k}$$

(3.23)

Por definição, f(X) = 1 se e somente se para algum k, tivermos:

$$S_{m_k} \le \sum_{j=1}^n x_j \le S_{m_k} \tag{3.24}$$

Na segunda camada  $\sum_{j=1}^n x_j$  é comparado com  $T_k = S_{m_k}$  e  $t_k = s_{m_k}$  para cada k. Como  $s_{m_i} \leq \sum_{j=1}^n x_j \leq S_{m_i}$ , o valor da saída da segunda camada  $(Q_k, q_k)$  pode ser visto como sendo:

$$Q_k + q_k = \begin{cases} 2 & \text{se } k = i \\ 1 & \text{se } k \neq i \end{cases}$$

(3.25)

Portanto, o elemento de saída da terceira camada é:

$$\operatorname{sgn}\left(\sum_{k=1}^{l} 2(Q_k + q_k) - 2l - 1\right) = \operatorname{sgn}(2l + 2 - 2l - 1) = 1$$

(3.26)

Similarmente, se f(X)=0, então não existe k tal que  $s_{m_k} \leq \sum_{j=1}^n x_j \leq S_{m_k}$ . Portanto,  $Q_k+q_k=1$  para todo k e a porta da terceira camada calcula:

$$\operatorname{sgn}\left(\sum_{k=1}^{l} 2(Q_k + q_k) - 2l - 1\right) = \operatorname{sgn}(2l - 2l - 1) = 0$$

(3.27)

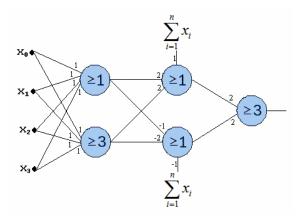

Portanto, o circuito fornece a saída correta para qualquer entrada  $X=(x_1,...,x_n)$ . A primeira camada do circuito consiste em d elementos. A segunda camada possui  $2l \le \left\lceil \frac{n}{d} \right\rceil + 1$  portas e a terceira apenas uma porta. Como  $d=\sqrt{n}$ , então o tamanho do circuito de 3 camadas é de  $2\sqrt{n}+1$  portas de limiar linear.

Na figura 3.7, a seguir, é mostrado um diagrama de implementação de um circuito que calcula a paridade de 4 variáveis utilizando um circuito de 3 camadas com 5 portas de limiar linear. Observe que, embora esse circuito de três camadas necessite de 5 portas e o da figura 3.6 necessite de 3, quando o número de entradas aumentar, o circuito de 3 camadas necessitará de menos portas. Por exemplo, se o número de entradas for 36, então o circuito de 2 camadas necessitará de 19 portas, enquanto que o circuito de 3 camadas necessitará de 13.

Figura 3.7 – Paridade de 4 variáveis com circuito de 3 camadas, construído com a técnica telescópica.

#### 3.5 – Implementação de Operações Aritméticas

Algumas funções booleanas, tais como adição e multiplicação, só podem ser calculadas utilizando as portas AON com número de camadas fixas em d se o tamanho aumentar exponencialmente. Isso resulta em uma área de *chip* que também aumenta exponencialmente [33]. Para que o tamanho do chip aumente polinomialmente, é necessário projetar circuitos com retardo não fixo o que acarreta em circuitos mais lentos e, portanto, ineficientes para algumas aplicações.

Com o uso de redes neurais é possível obter circuitos com profundidade fixa e tamanho polinomial. A seguir, são mostrados alguns exemplos de operações aritméticas implementadas com redes neurais discretas.

#### 3.5.1 – Adição

Para um somador de dois números de 2 bits,  $X = \{x_1, x_0\}$  e  $Y = \{y_1, y_0\}$ , é possível calcular a soma Z = X + Y utilizando um circuito de limiar linear com 2 camadas.

Inicialmente, é necessário encontrar os intervalos em que a função seja igual a 1, como mostrado na tabela 3.1.

| $(x_1,x_0)$ | $(y_1,y_0)$ | $soma(z_2 z_1 z_0)$ | $(x_1,x_0)$ | $(y_1,y_0)$ | $soma(z_2 z_1 z_0)$ |

|-------------|-------------|---------------------|-------------|-------------|---------------------|

| 00          | 00          | 000=0               | 10          | 00          | 010=2               |

| 00          | 01          | 001=1               | 10          | 01          | 011=3               |

| 00          | 10          | 010=2               | 10          | 10          | 100=4               |

| 00          | 11          | 011=3               | 10          | 11          | 101=5               |

| 01          | 00          | 001=1               | 11          | 00          | 011=3               |

| 01          | 01          | 010=2               | 11          | 01          | 100=4               |

| 01          | 10          | 011=3               | 11          | 10          | 101=5               |

| 01          | 11          | 100=4               | 11          | 11          | 110=6               |

Tabela 3.1 – Soma de dois números de 2 bits.

Note que o peso de  $x_1$  e  $y_1$  é 2 e o peso de  $x_0$  e  $y_0$  é 1. Separando os resultados em que cada  $z_i$  é 1, tem-se:

- Bit  $z_0 \to Os$  resultados em que  $z_0$  é 1 são: 1, 3 e 5. Mas como  $z_0$  é função, apenas de  $x_0$  e  $y_0$ , então é utilizado apenas o resultado 1;

- Bit  $z_1 \rightarrow \text{Resultados 2, 3 e 6}$ ;

- Bit  $z_2 \rightarrow \text{Resultados 4, 5 e 6}$ ;

Assim, as portas da primeira camada podem ser implementadas da seguinte forma:

• Bit 1

$$y_0 = \text{sgn}\left(\sum_{i=1}^n w_i x_i - 1\right)$$

(3.28)

$$\bar{y}_0 = \text{sgn}\left(1 - \sum_{i=1}^n w_i x_i\right)$$

(3.29)

$$z_0 = \operatorname{sgn}(y_0 + \bar{y}_0 - 2) \tag{3.30}$$

• Bit 2

$$y_1 = \text{sgn}\left(\sum_{i=1}^n w_i x_i - 2\right)$$

(3.31)

$$\overline{y}_1 = \operatorname{sgn}\left(3 - \sum_{i=1}^n w_i x_i\right) \tag{3.32}$$

$$z_1 = \text{sgn}(y_1 + \overline{y}_1 - 2) \tag{3.33}$$

• Bit 3

$$y_2 = \text{sgn}\left(\sum_{i=1}^n w_i x_i - 4\right)$$

(3.34)

$$\overline{y}_2 = \operatorname{sgn}\left(6 - \sum_{i=1}^n w_i x_i\right) \tag{3.35}$$

$$z_2 = \text{sgn}(y_2 + \bar{y}_2 - 2) \tag{3.36}$$

Para implementar esse somador são utilizadas 9 portas neurais, enquanto que, se utilizada a lógica tradicional seriam necessárias 27 portas. Embora, tanto o somador implementado com a lógica tradicional quanto o somador implementado com a lógica neural possuam número de camadas constantes, apenas o somador implementado com a lógica neural possui tamanho polinomial.

#### 3.5.2 – Multiplicação

A multiplicação de *n* bits pode ser dividida em três etapas, como mostrado na figura 3.8.

Figura 3.8 – Bloco funcional do multiplicador.

O primeiro bloco calcula apenas o produto de cada bit de uma entrada com cada bit da outra entrada. O segundo bloco utiliza a técnica *block-save*, que é um aprimoramento da técnica já conhecida como *carry-save*, para implementar circuitos que executem a adição. O terceiro bloco é uma adição propriamente dita.

#### Bloco I - AND

A multiplicação pode ser reduzida em uma soma múltipla. Seja  $X=x_{n-1}x_{n-2}\cdots x_0$  e  $Y=y_{n-1}y_{n-2}\cdots y_0$  dois números de n bits. O produto  $Z=X\cdot Y$  é dado por:

$$Z = \sum_{i=0}^{n-1} z_{i_{2n-1}} z_{i_{2n-2}} \cdots z_{i_0}$$

(3.37)

para i = 0, ..., n-1 e

$$z_{i} = \underbrace{0 \cdots 0}_{n-i} (x_{n-1} \wedge y_{i})(x_{n-2} \wedge y_{i}) \cdots (x_{0} \wedge y_{i}) \underbrace{0 \cdots 0}_{i}$$

(3.38)

Utilizando uma porta de limiar linear, para implementar a lógica AND da equação 3.38, seriam necessárias  $n^2$  portas para calcular todos os  $z_i$ 's. Portanto, a multiplicação foi reduzida a uma soma de n números de 2n bits.

#### • Bloco II – Técnica *Block-Save*

A principal dificuldade no cálculo de uma soma com uma grande quantidade de números é o cálculo do bit de *carry* em paralelo. A tradicional técnica *carry-save* reduz a soma de três números em uma soma de dois números em um único passo.

Sejam três números  $X=x_{n-1}x_{n-2}...x_0$ ,  $Y=y_{n-1}y_{n-2}...y_0$  e  $Z=z_{n-1}z_{n-2}...z_0$  todos em representação binária. O *i*-ésimo bit de cada número pode ser somado, resultando em  $x_i+y_i+z_i=2c_{i+1}+w_i$ , em que  $c_{i+1}$  é o bit de *carry* gerado pela soma dos *i*-ésimos bits  $x_i$ ,  $y_i$  e  $z_i$ . Dessa forma, tem-se X+Y+Z=C+W, em que  $C=c_n\,c_{n-1}...c_0$  com  $c_0=0$  e  $W=w_{n-1}\,w_{n-2}...w_0$ . Note que  $c_{i+1}=x_iy_i\vee y_iz_i\vee z_ix_i$  e  $w_i=x_i\oplus y_i\oplus z_i$ , portanto, os  $c_{i+1}$  e  $w_i$  podem ser calculados paralelamente em um único passo. Por exemplo, seja X=1001, Y=0111 e Z=1101, assim C=11010 e W=0011.

A técnica *block-save* é um aprimoramento da técnica *carry-save*. Ela reduz a soma de n números O(n) bit para uma soma de dois números de O(n) bit em um único passo. A técnica *block-save* é apresentada por meio de um exemplo em que os n números do somatório possuem n bits.

Escrevendo cada um dos n bits como sendo  $x_i = x_{i_{n-1}} x_{i_{n-2}} \dots x_{i_0}$ , para  $i = 1, \dots, n$ . Para simplificar, assumiremos que ao invés de termos n inteiros de n bits cada, teremos n inteiros com  $n/(\log n)$  bits, e fazendo  $N = n/\log n$ . Separando cada número binário  $x_i$  em N blocos consecutivos de  $\widetilde{x}_{i_0}, \widetilde{x}_{i_1}, \dots, \widetilde{x}_{i_{N-i}}$  para cada  $(\log n)$  bits, teremos:

$$x_{i} = \sum_{j=0}^{N-1} \widetilde{x}_{i_{j}} \cdot 2^{\log n \cdot j}$$

(3.39)

em que  $0 \le \widetilde{x}_{i_j} < 2^{\log n}$ . Logo, a soma total, depois de reorganizados os índices do somatório, será:

$$S = \sum_{i=1}^{n} x_{i} = \sum_{j=0}^{N-1} \left( \sum_{i=1}^{n} \widetilde{x}_{i_{j}} \right) \cdot 2^{\log n \cdot j}$$

(3.40)

Observe que para cada j=0,...,N-1, a soma de cada bloco  $\widetilde{s}_j$  será:

$$\widetilde{s}_j = \sum_{i=1}^n \widetilde{x}_{i_j} < \sum_{i=1}^n 2^{\log n \cdot j} = 2^{2\log n}$$

(3.41)

Portanto,  $\widetilde{s}_j$  pode ser representado por  $2\log n$  bits. Então, cada bloco de somas  $\widetilde{s}_j$  pode ser expresso por:

$$\widetilde{s}_{i} = \widetilde{c}_{i+1} 2^{\log n} + \widetilde{w}_{i} \tag{3.42}$$

em que  $0 \le \widetilde{c}_{j+1} < 2^{\log n}$  são os  $(\log n)$  bits do *carry* das somas  $\widetilde{s}_j$  com  $\widetilde{c}_0 = 0$  e  $\widetilde{w}_j < 2^{\log n}$ . Assim, tem-se:

$$S = \sum_{j=0}^{N-1} \left( \sum_{i=1}^{n} \widetilde{x}_{i_{j}} \right) \cdot 2^{\log n \cdot j}$$

$$= \sum_{j=0}^{N-1} \widetilde{s}_{j} 2^{\log n \cdot j}$$

$$= \sum_{i=0}^{N-1} \widetilde{c}_{j+1} 2^{(j+1)\log n} + \sum_{i=0}^{N-1} \widetilde{w}_{j} 2^{j\log n}$$

(3.43)

Desde que ambos os  $\widetilde{c}_{j+1}$  e  $\widetilde{w}_j$  sejam  $< 2^{\log n}$ , a representação binária de  $\sum_{j=0}^{N-1} \widetilde{c}_{j+1} 2^{(j+1)\log n}$  é simplesmente a concatenação dos bits  $\widetilde{c}_N \, \widetilde{c}_{N-1} \cdots c_0$ . Similarmente, concatenando os bits  $\widetilde{w}_{N-1} \cdots \widetilde{w}_0$  para a representação binária de  $\sum_{j=0}^{N-1} \widetilde{w}_j 2^{j\log n}$ . Logo, pode ser observado que ocorre uma redução na soma de n números de n bits para a soma de dois números de O(n) bits. Além disso, ao calcular todos os  $\widetilde{c}_j$  e  $\widetilde{w}_j$  em paralelo, é obtido como resultado dois números.

Só resta mostrar como calcular a representação em  $2\log n$  bits de cada bloco de somatório  $\widetilde{s}_j = \widetilde{c}_{j+1} 2^{\log n} + \widetilde{w}_j$ . Desde que cada número de somas seja da forma  $\sum_{k=0}^{\log n-1} 2^k x_k < n$ , a soma total é um polinômio limitado em somas de  $n\log n$  variáveis  $x_i$ , em que  $1 \le i \le n$  e  $(j-1)\log n < 1 \le j\log n$ . Assim, cada bit de  $\widetilde{c}_{j+1}$  e  $\widetilde{w}_j$  é uma função polinomial limitada em  $n\log n$  variáveis. Em outras palavras, cada bit  $\widetilde{c}_{j+1}$  e  $\widetilde{w}_j$  é uma função simétrica generalizada. Portanto, segue que cada bit do bloco de soma de  $\widetilde{s}_j$  pode ser representado como uma soma de polinômios com variáveis em  $x_{i_j}$ .

Na figura 3.9 é mostrado a técnica *block-save* calculando a soma de quatro inteiros de 16 bits. Como n = 16, a soma múltipla é dividida em 4 colunas.

Figura 3.9 – Exemplo de cálculo da soma múltipla usando a técnica *block-save*.

Assim cada coluna é somada separadamente da seguinte forma:

- Zerando as colunas pares, são somados os n números e o resultado armazenado em  $z_{impar}$ .

- Zerando as colunas ímpares, são somados os n números e o resultado armazenado em  $z_{nar}$ .

Pode-se calcular  $z_{par}$  e  $z_{impar}$  utilizando um circuito de limiar linear de duas camadas.

• Bloco III – Soma de 2 números

Por fim, o bloco restante calcula a soma de  $z_{par} + z_{impar}$ , como mostrado na figura 3.10. É necessário um circuito de 2 camadas para calcular essa soma.

Figura 3.10 – Esquema de cálculo da soma múltipla usando a técnica *block-save*.

Portanto a multiplicação de dois números de n bits pode ser realizada com um circuito de limiar linear de 5 camadas, em que a primeira calcula o produto (AND lógico), bit a bit, entre os dois valores da entrada; a segunda e a terceira calcula  $z_{par}$  e  $z_{impar}$ ; e a quarta e quinta calcula a soma  $z_{par} + z_{impar}$ . Considerando que a soma múltipla é uma combinação linear entre a segunda e a terceira camada [33], pode-se conectar um somador na saída da terceira camada, dessa forma só são necessárias quatro camadas para calcular a multiplicação.

#### 3.6 – Conclusão

Neste capítulo foi apresentada a arquitetura da rede neural utilizada na implementação do multiplicador em corpos finitos. As portas de limiar linear, que é a estrutura básica dessa rede, possuem as portas tradicionais (AND, OR e NOT) como subconjunto, o que resulta em uma grande vantagem.

Para extrair todas as vantagens das portas de limiar linear, como a diminuição da complexidade espacial de funções simétricas de exponencial para polinomial, são utilizadas estruturas específicas, que fazem uso de técnicas algébricas, para construir circuitos de limiar linear. Por exemplo, a função paridade, que requer  $2^{n-1} + 1$  portas AON, pode ser calculada utilizando  $\left\lceil \frac{n}{2} \right\rceil + 1$  portas de limiar linear. Ambas as arquiteturas possuem retardo equivalente a 2 portas. Caso seja necessário uma diminuição do número de portas é possível utilizar um circuito com retardo igual a 3 que implementaria a paridade com  $2\sqrt{n} + 1$  portas.

Essa potencialidade das portas de limiar linear, já é bem explorada em aplicações de adição, multiplicação e divisão em aritmética tradicional [18,19]. A possibilidade de utilizar essa potencialidade em outros sistemas numéricos tais como os corpos finitos, pode resultar em uma poderosa ferramenta na busca de circuitos mais eficientes no cálculo de operações aritméticas complexas.

# 4. Implementação do Multiplicador GF(2<sup>4</sup>) com Portas de Limiar Linear

#### 4.1 - Introdução

Como visto no capítulo 2, o multiplicador de Mastrovito possui uma das menores complexidades espaciais e temporais dentre os multiplicadores em paralelo, portanto sua arquitetura é a mais adequada para ser implementada com redes neurais discretas. Nesse capítulo é apresentada uma arquitetura de multiplicador em corpo finito utilizando portas de limiar linear como elemento de processamento. Inicialmente será projetado um multiplicador GF(2<sup>4</sup>) com portas lógicas tradicionais, em seguida é feito o projeto do multiplicador GF(2<sup>4</sup>) utilizando portas de limiar linear, desse modo será possível realizar uma comparação entre as duas arquiteturas.

#### 4.2 - Multiplicador de Mastrovito com Portas AON

Como visto no capítulo 2, o multiplicador de Mastrovito é implementado em duas etapas: a multiplicação polinomial e a redução módulo p(x). Essas etapas são detalhadas a seguir.

#### 4.2.1 – Multiplicação Polinomial Ordinária

Considere A(x) e B(x) polinômios em  $GF(2^n)$ . A multiplicação  $A(x) \cdot B(x)$  é dada por:

$$C(x) = A(x) \cdot B(x) \bmod p(x) \tag{4.1}$$

A equação 4.1 pode ser reescrita como:

$$C(x) = C'(x) \bmod p(x) \tag{4.2}$$

Dessa forma, tem-se:

$$C'(x) = c'_0 + c'_1 x + c'_2 x^2 + \dots + c'_{2n-2} x^{2n-2}$$

(4.3)

Em que cada elemento  $c'_i$  é dado por:

$$c'_{j} = \begin{cases} \sum_{i=0}^{j} a_{i}b_{j-i} & para \ j < n \\ \sum_{i=j-n+1}^{n-1} a_{i}b_{2n-j-1} & para \ j \ge n \end{cases}$$

$$(4.4)$$

Independentemente do polinômio p(x) escolhido, são necessárias  $n^2$  portas AND para calcular todos os  $a_ib_j$ , em que i=1,...,n e j=1,...,n. Para cada  $c_j$ , o número de elementos no somatório da equação 4.4 é dado por:

$$\begin{cases}

(j+1) \text{ elementos} & \text{para } j < n \\

(2n-j-1) \text{ elementos} & \text{para } j \ge n

\end{cases}$$

(4.5)

Como visto na seção 3.5, para implementar a função paridade com n variáveis e fan-in ilimitado são necessárias  $2^{n-1}+1$  portas AON e retardo constante e igual a  $2\tau_{AON}$ , em que  $\tau_{AON}$  corresponde ao retardo de uma porta lógica tradicional. Seja #AON o número de portas AON. Como cada  $c'_i$  é obtido a partir de um somatório de elementos, então o número de portas AON necessárias para obter os coeficientes  $c'_i$  é:

$$#AON = \sum_{j=1}^{n-1} (2^{j} + 1) + \sum_{j=n}^{2n-3} (2^{2n-j-2} + 1)$$

$$= (n-1) + \sum_{j=1}^{n-1} 2^{j} + (n-2) + 2^{2n-2} \sum_{j=n}^{2n-3} 2^{-j}$$

$$= (2n-3) + 2^{n} - 2 + 2^{2n-2} \left( \frac{2^{2n-2} - 1}{2^{2n-3}} - \frac{2^{n} - 1}{2^{n-1}} \right)$$

$$= 2n - 5 + 2^{n} + 2^{2n-1} - 2 - 2^{2n-1} + 2^{n-1}$$

$$= 2n - 7 + 2^{n-1} (2+1)$$

$$#AON = 3 \cdot 2^{n-1} + 2n - 7$$

$$(4.6)$$

Considerando a operação AND bit a bit inicial, que necessita de  $n^2$  portas, o número total de portas para executar a multiplicação polinomial convencional é:

$$#AON = 3 \cdot 2^{n-1} + n^2 + 2n - 7 \tag{4.7}$$

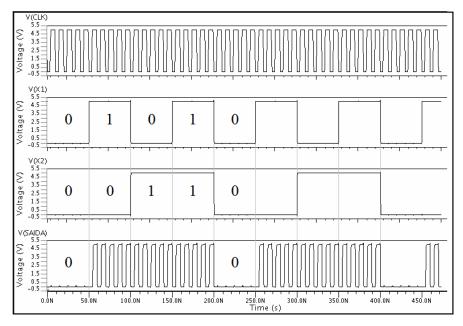

O retardo da multiplicação polinomial convencional é  $1\tau_{AON}$  para o AND bit a bit e  $2\tau_{AON}$  para as somas dos coeficientes, assumindo *fan-in* ilimitado.