# "ANTEPROJETO DE UM CONVERSOR D/A MONOLÍTICO, 32 CANAIS COM TECNOLOGIA BIPOLAR PARA USO EM SISTEMA MCP-LEI A"

#### Galdenoro Botura Jr. - UNESP/FEG/LED

Faculdade de Engenharia de Guaratinguetá - C.P. 205 - 12500 Guaratinguetá-SP Fone: (0125) 22-2800

Alberto M. Jorge e José Antonio S. Dias - UNICMAP/FEE/LED

LED/FEE/UNICAMP - C.P. 6061 - 13081 Campinas-SP - Fone: (0192) 39-1301 ramal 2500

## SUMÁRIO

Este trabalho versa sobre o projeto de um conversor D/A por Modulação de Código de Pulso (MCP) - Lei A - 32 ca nais. É apresentada a topologia de conversão, o projeto, os circuitos e as máscaras de integração que permitem a obtenção de resultados satisfatórios, dentro das especificações exigidas para projetos desta natureza. Realiza-se, ain da, uma rápida discussão em torno dos motivos que ocasionaram as modificações introduzidas na topologia do conversor em relação às arquiteturas clássicas.

# 1. INTRODUÇÃO

No desenvolvimento do projeto de um conversor p/A não linear de modulação por código de puldo (MCP), a obtenção do valor final do nível de sinal decodificado pode ser feita de várias maneiras, como pode ser visto nas publicações especializadas durante a década passada e no início desta década. Uma interessante forma de se obter uma topologia de decodificação a partir de um simples equacionamento da lei-A, 128 segmentos, foi proposta por Kaneko |1|. A partir deste equacionamento, foi colocada uma nova configuração de estrutura |2| onde os amplificadores chaveados foram substituido por um circuito multiplicador linear.

Este trabalho mostra, a partir do equacionamen to feito em |1| e a topologia desenvolvida em |2|, uma nova estrutura de obtenção dos valores desejados.

A substituição dos dois conversores D/A, um de 6 "bits" e outro de 7 "bits", utilizados em |2| por três conversores D/As, um de 6 "bits" e dois de 4 "bits", é apresentado e uma discussão sobre as vantagens do uso desta nova topologia é feita. É apresentado, ainda, o projeto e "layout" dos conversores de 4 e 6 "bits" e do circuito lógico combinacional exigido.

## 2. CONCEITUAÇÃO

A expressão geral da decodificação, para a lei-A, 128 segmentos, feita em |1| é:

Este trabalho contou com o apoio financeiro da FINEP.

$$y(L,V) = \Delta(L)(V+P)$$

(1)

Sendo:

L : número de ordem do segmento, sendo M segmentos, L  $\epsilon$  {0,1,2, ..., M-L};

$\forall$  : número real que exprime o nível expandido dentro do segmento;  $\forall$   $\epsilon$   $\{\phi,N\}$ ;

M(L): intervalo entre os níveis discretos de cada seg mento;

com relação ainda a |1| tem-se que:

$$\Delta(L) = 2^{1-\eta} \tag{2}$$

$$P = N.\eta + b \tag{3}$$

Onde:

$\eta$  : vale  $\phi$  ou 1, conforme L valha zero ou seja diferente de zero;

N : número de níveis discretos de cada segmento;

b : deslocamento do nível zero; a necessidade de seu em prego advém da diminuição conseguida por este inter médio, do erro médio quadrático de quantização.

De (1), (2) e (3) tira-se que:

$$v(L,V) = (2^{1-\eta})(V + N, \eta + b)$$

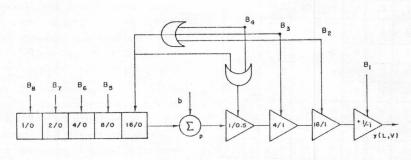

A expressão citada conduz diretamente ao diagra ma em bloco apresentado na figura 1.

Neste diagrama tem-se o valor de "V" sendo obt<u>i</u> do através do acionamento, executado pelos "bits"  $B_5$ ,  $B_6$ ,  $B_7$ ,  $B_8$ , de um decodificador linear, que possui, ain da, um quinto bloco, que é acionado por n, conseguindo-

se em sua saída a adição de (V + N.ŋ). Em seguida o va lor de "b" é acionado e o resultado multiplicado por um amplificador chaveado de 3 estágios, segundo os valores de  $B_2$ ,  $B_3$  e  $B_4$ , que fornecem a identificação do segmen to. A polaridade é, enfim, obtida pelo comando  $B_1$  no inversor chaveado no último estágio.

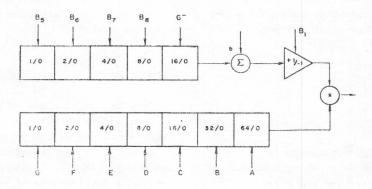

Em |2|, o autor substitui os amplificadores cha veados por um multiplicador e um conversor D/A de 7 "bits". Assim miltiplica-se o valor de  $\Delta(L)$  por  $(V+N.\eta+b)$  para se obter o sinal decodificado. A polaridade de saída é também obtida por intermédio de um inversor.

#### 3. TOPOLOGIA

A proposta aqui apresentada é a substituição do decodificador D/A de 7 "bits", responsável pela geração de  $\Delta(L)$ , por dois de 4 "bits" e a inserção do bloco de chaveamento de polaridade diretamente na estrutura do multiplicador, como mostrado na referência |3|.

Esta proposta é fundamentada em princípio bas tante simples, explicado a seguir, e que permite, atra vés da substituição mencionada, a eliminação da maior parte dos erros introduzidos pela conversor de 7 "bits".

Os valores que  $\Delta\left(L\right)$  podem assumir são determina dos pela equação (2) e valem

$$\Delta(L) = 2^{L-\eta}$$

,  $L \in \{0,1,3,...,7\}$

$$\eta = \begin{cases} 0 \text{ para } L = 0, \\ 1 \text{ para } L \neq 0, \end{cases}$$

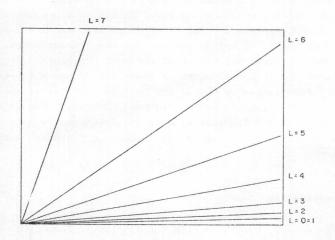

ou seja, o valor de  $\Delta(L)$  para L=0 é idêntico a  $\Delta(L)$  para L=1. O fator  $\Delta(L)$  é responsável pela variação da inclinação dos segmentos na Lei-A. Assim,  $\Delta(L)_0 = \Delta(L)_1$  significa que os dois primeiros segmentos possuem as mesmas inclinações e podem ser considerados como um só. Este fato pode ser representado graficamente, como se apresenta na figura 3.

Nesta, "L" corresponde aos diversos segmentos existentes e A(L) é a inclinação do segmento em relação à horizontal. Assim, pode-se considerar somente a existência de 7 segmentos no total.

Por característica de decodificação, a relação entre dois valores de  $\Delta(L)$  adjacentes é dois, isto nos possibilita a obtenção deste valor pelo produto e pela divisão por este número. Assim tem-se:

$$\Delta(L)_{L-2} = \frac{1}{2} \Delta(L)_{L-1} \tag{4}$$

A existência de um número ímpar de segmentos possibilita a fixação de um segmento central, que no caso de 7 segmentos é o 49, para a definição de uma referência na mudança de conduta na obtenção de  $\Delta(L)$ . Assim, definiu-se que os 3 segmentos inferiores ao 49 segmento seriam obtidos por divisão e os 3 superiores

pelo produto. Deste modo Δ(L) valerá:

$$\Delta(L) = \Delta(L)_{4} \cdot (2)^{n-m}$$

(5)

Sendo

$$n = \begin{cases} L - 4 & para \ 4 < L < 7 \\ 0 & para \ 1 < L < 3 \end{cases}$$

$$n = \begin{cases} 0 & para \ 4 < L < 7 \\ 4 - L & para \ 1 < L < 3 \end{cases}$$

De 5, pode-se levantar os valores de  $\Delta$ (L) para os sete casos possíveis e constatar que  $\Delta$ (L) variará dentro da faixa especificada.

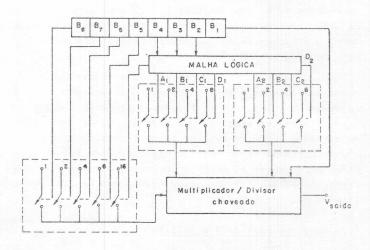

Um diagrama em blocos desta nova topologia é mostrado na figura 4.

Neste diagrama, o multiplicador-divisor chavea do recebe os sinais das 3 D/As lineares juntamente com o "bit" de polaridade e determina a partir destes sinais os valores que a saída assumirá. A topologia, por tanto, apresenta 3 blocos básicos:

- l: bloco lógico; constituído do registrador de deslocamento, memória e malha lógicas;

- 2: conversor D/A de 4 e 6 "bits";

- 6: multiplicador-divisor chaveado.

# 4. BLOCO LÓGICO DECODIFICADOR

Este bloco tem função de fazer a decodificação do sinal recebido da memória e comandar os conversores D/A que definem o segmento. Para a definição dos parâ metros envolvidos no projeto lógico deste bloco é essencial um rápido comentário sobre o princípio de multiplicação-divisão utilizado no MCP.

Um circuito integrado multiplicador-divisor |3| com algumas modificações em relação a referência citada é utilizado na parte analógica do sistema. A corrente na saída da célula multiplicadora vale

$$I_{X} = \frac{I_{M} \cdot I_{O}}{I_{D}}$$

(6)

onde:

$I_{x}$  = corrente de saída da célula multiplicadora;

I<sub>M</sub> = corrente a ser multiplicada;

I<sub>R</sub> = corrente a ser dividida;

I = corrente de referência.

O uso ora de "I<sub>M</sub>", ora de "I<sub>R</sub>", como corrente de referência permite a obtenção do efeito multiplicação-divisão desejado.

A opção de uma configuração 3 + 1 ao invés da convencional de 4 "bits", para os D/As estabelece quais devem ser as chaves que serão comutadas na definição de cada valor. Assim, no projeto em questão todos

Baseando-se nas observações apresentadas, construiu-se diretamente a Tabela Verdade do bloco lógico decodificador, não se esquecendo ainda que, neste caso, o primeiro e o segundo segmentos são coincidentes e que a variação do nível entre 0 e 16 só ocorre no primeiro nível.

Tabela I - Tabela Verdade da malha lógica.

| B <sub>4</sub> | В3 | B <sub>-2</sub> | Gerador 1      |                |                |    | Gerador 2      |                |                |                | G |

|----------------|----|-----------------|----------------|----------------|----------------|----|----------------|----------------|----------------|----------------|---|

|                |    |                 | A <sub>1</sub> | B <sub>1</sub> | c <sub>1</sub> | D1 | A <sub>2</sub> | B <sub>1</sub> | c <sub>2</sub> | D <sub>2</sub> |   |

| 0              | 0  | 0               | 1              | 0              | 0              | 0  | 1              | 1              | 1              | 1              | 0 |

| 0              | 0  | 1               | 1              | 0              | 0              | 0  | 1              | 1              | 1              | 1              | 1 |

| 0              | 1  | 0               | 1              | 0              | 0              | 0  | 0              | 0              | 1              | 0              | 1 |

| 0              | 1  | 1               | 1              | 0              | 0              | 0  | 0              | 1              | 0              | 0              | 1 |

| 1              | 0  | 0               | 1              | 0              | 0              | 0  | 1              | 0              | 0              | 0              | 1 |

| 1              | 0  | 1               | 0              | 1              | 0              | 0  | 1              | 0              | 0              | 0              | 1 |

| 1              | 1  | 0               | 0              | 0              | 1              | 0  | 1              | 0              | 0              | 0              | 1 |

| 1              | 1  | 1               | 1              | 1              | 1              | 1  | 1              | 0              | 0              | 0              | 1 |

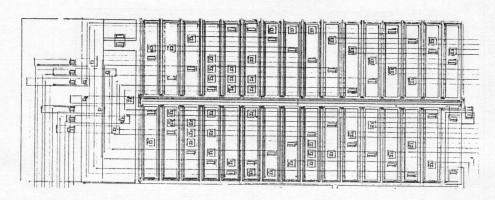

A partir da Tabela Verdade, projetou-se o circuito digital equivalente que serviu de base para o projeto do circuito I<sup>2</sup>L e posteriormente a confecção do Layout deste bloco (figura 5).

# 5. CONVERSORES D/A

# 5.1. Estrutura Básica de Conversão

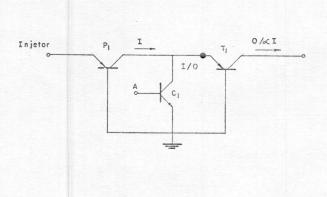

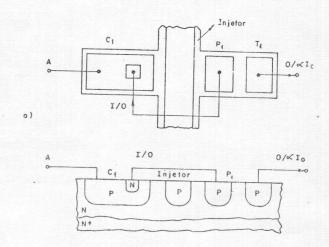

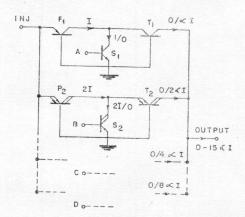

A concepção estrutural dos conversores |4| par tiu da premissa de que consegue-se a obtenção de corren tes de valores múltiplos a partir de uma célula  $I^2L$  com um transistor PNP (figura 6 e 7).

O injetor permanentemente introduz uma corrente no emissor de P $_1$  e na base de C $_1$ . Quando o ponto A es tá alto, o transistor C $_1$  conduz e a corrente do coletor de P $_1$  é direcionada para a terra, fazendo com que  $^{\rm I}$ C1 seja igual a zero.

Quando o ponto A está baixo, o transistor  $C_1$  permanece cortado e toda a corrente do emissor de  $P_1$  é injetada no coletor de  $T_1$  e consequentemente, em seu coletor fluirá uma corrente que será  $\alpha I$ , sendo  $\alpha$  o ganho de corrente de um transistor na configuração base comum. A possibilidade de se obter transistores de até 4 coletores permite que se consiga correntes com valores  $m \bar{u}_1$  tiplos de I, a partir de associação dessas configurações (figura 8).

# 5.2. Conversor D/A de 4 e 6 "Bits"

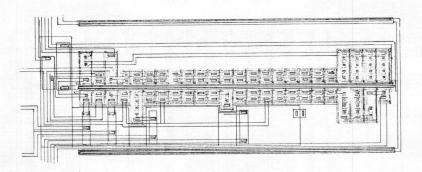

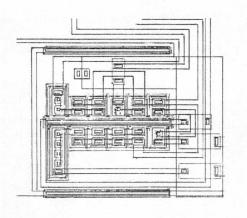

As figuras 5 e 6 apresentam o "layout", confeccionado com o uso do EDMAS, de um conversor de 4 e  $o\underline{u}$

tro de 6 "bits".

Nestes conversores verifica-se a necessidade de um transistor PNP para cada coletor da estrutura  $\rm I^2L$  existente. Deste modo, tem-se que cada transistor  $\rm I^2L$  comanda, no máximo, 4 transistores PNP.

Na confecção do "layout", tomou-se o cuidado de procurar a melhor distribuição possível dos transistores ao longo da fita injetora, pois a variação do potencial ao longo desta tem influência marcante no valor da corrente de saída. Neste projeto procurou-se equalizar o potencial ao longo da fita através da colocação dos transistores de comando (I<sup>2</sup>L) e dos transistores de corrente (PNP) lado a lado, e não mais do lado oposto a da fita (frente a frente) como foi posicionado em |2|e|4|. Através deste procedimento conseguiu-se projetar uma fita injetora na qual o nível de metal não sofre interrupções para a interligação dos transistores.

Um outro ponto importante e que, se não estudado com o devido cuidado, produz erros consideráveis no valor da corrente de saída é a distribuição dos poten ciais no substrato da lâmina, originados em função da resistividade do material e das correntes em direção ao ponto de terra dos conversores.

Procurou-se prevenir este problema através de uma difusão produnda do tipo N+, que faz contato com o substrato. Deste modo, consegue-se que as correntes fluam sempre em direção aos contatos de um modo perpendicular a eles.

## CONCLUSÃO

A substituição de um conversor D/A de 7 "bits" por dois de 4 "bits" minimiza os erros introduzidos por este conversor na função de transferência. Erro este que contribui decisivamente no final de cada segmento, onde o problema se torna mais crítico. O possível au mento da complexidade da estrutura do circuito multipli cador, pois agora existe a necessidade de se obter tam bém a divisão, é facilmente contornado, uma vez que es ta operação está normalmente presente na maior dos projetos desses circuitos. As modificações introdu zidas no projeto dos conversores, contribuem para que estes tenham um melhor desempenho, aumentando, assim, a confiabilidade dos resutados obtidos. Finalmente, espe ramos que as modificações introduzidas venham a ser tão eficazes quanto os resultados obtidos em simulações (SPICE II) contribuindo assim para que esta topologia constitua uma alternativa bastante interessante para os projetistas de circuitos integrados que atuam nesta

# REFERÊNCIAS

|1| Kaneko, H., "A Unified Formulation of Segmente Companding Laws and Synthesis of Codec in Digital Compandors", the Bell System Tecnical Journal. Vol. 49, no 7, pp. 1555-1983, setembro de 1970.

- |2| Jorge, A.M., "Ensaio no Projeto e Construção de um Decodificador D/A, MCP, com Técnica I<sup>2</sup>L", tese de Doutorado UNICAMP, junho de 1982.

- |3| Botura, Jr., G., "Projeto de um Multiplicador Chaveado", tese de Mestrado, UNICAMP, junho de 1985.

- |4| Hart, C.M., et all., "Bipolar LSI Take, A New Direction With Integrated Injection Logic", Electronics, Vol. 47, no 20, pp. 111-118, 3 de outubro de 1974.

## FIGURAS

Figura 1 - Diagrama em bloco do sistema decodificador para lei-A, 128, |1|.

Figura 2 - Sistema decodificador utilizando o principio da multiplicação |2|.

Figura 3 - Representação gráfica de L e  $\Delta(L)$ .

Figura 4 - Sistema decodificador utilizando o princípio multiple cação-divisão com 3 conversores D/As.

Figura 5 - "Layout" do bloco lógico decodificador.

Figura 6 - Célula básica, composta de um transistor  $I^2L$  e um transistor PNP.

Figura 7 - a) Vista superior; vista em corte. b) Estrutura da célula básica.

Figura 8 - Associação de estruturas com a finalidade de obtenção de correntes com valores múltiplos a  $\it l$ .

Figura 9 - "Layout" do conversor de 6 "bits".

Figura 10 - "Layout" do conversor de 4 "bits".