# Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Departamento de Engenharia Elétrica

#### Trabalho de Conclusão de Curso

# DESIGN E VERIFICAÇÃO FUNCIONAL DE UM BLOCO I<sup>2</sup>C CONTROLLER

Heriberto Gomes da Fonseca Junior

Campina Grande - PB Junho de 2023

#### Heriberto Gomes da Fonseca Junior

# DESIGN E VERIFICAÇÃO FUNCIONAL DE UM BLOCO I<sup>2</sup>C CONTROLLER

Trabalho de Conclusão de Curso submetido à Coordenação de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Engenheiro Eletricista.

Universidade Federal de Campina Grande - UFCG

Centro de Engenharia Elétrica e Informática - CEEI

Departamento de Engenharia Elétrica - DEE

Coordenação de Graduação em Engenharia Elétrica - CGEE

Gutemberg Gonçalves dos Santos Júnior, D.Sc. (Orientador)

Campina Grande - PB Junho de 2023

#### Heriberto Gomes da Fonseca Junior

#### DESIGN E VERIFICAÇÃO FUNCIONAL DE UM BLOCO I<sup>2</sup>C CONTROLLER

Trabalho de Conclusão de Curso submetido à Coordenação de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Engenheiro Eletricista.

Aprovado em \_\_\_\_ /\_\_\_ /\_\_\_\_

Marcos Ricardo Alcântara Morais Universidade Federal de Campina Grande Avaliador

#### Gutemberg Gonçalves dos Santos Júnior

Universidade Federal de Campina Grande Orientador

> Campina Grande - PB Junho de 2023

### Agradecimentos

Ao Senhor Deus, autor da fé e criador de todas as coisas, por me dar forças e me sustentar em todas as tribulações e intempéries vividas durante a minha vida.

A minha mãe Andréa, meu pai Heriberto e minha irmã Gabriela que fizeram com que esse sonho fosse possível e estiveram presente durante todas as etapas da minha formação.

A minha noiva e eterna companheira Ester, que sempre acreditou em mim e me amou em todos os momentos, decidiu viver um relacionamento a distância e superou esse desafio ao meu lado, fazendo com que todos esses anos fossem mais felizes e divertidos.

Aos amigos e irmãos que fiz durante a vida, que dividiram momentos alegres e tristes comigo. Em especial Alan Pessoa, Arthur Macena, Ezequiel Brito, Hélder Guimarães, Lucas Dechenier, Lourival Netto e Matheus Petrúcio que dividiram os anos de estudo e formação comigo, bem como suas dificuldades e barreiras. Espero que todos vocês estejam sempre comigo na jornada da vida e que possamos compartilhar muitos momentos.

A todos que fazem parte do laboratório XMEN em especial a Guilherme Martins e André Igor, por me incentivarem a realizar as atividades (inclusive esse trabalho) dentro do prazo e compartilharem conhecimentos em microeletrônica e boas risadas.

Aos professores que tive durante a minha formação, em especial os professores Gutemberg Júnior e Marcos Morais, por todas as portas abertas, pelos anos de ensinamentos e por terem sido meus tutores para minha carreira profissional.

Enfim, agradeço a todos que cruzaram meu caminho nessa graduação e que tive o prazer de ajudar e ser ajudado.

#### Resumo

Este trabalho tem como propósito o desenvolvimento (design digital) e a verificação funcional de um bloco  $I^2C$  controller, um componente crucial na comunicação de dados em sistemas embarcados. O protocolo  $I^2C$  é amplamente utilizado na indústria eletrônica para a interconexão de dispositivos integrados, e o bloco desempenha o papel de controlador principal nesse barramento. O objetivo deste projeto é projetar e verificar um bloco I<sup>2</sup>C controller, considerando aspectos de hardware e/ou software, como a definição da arquitetura, a interface de comunicação, a lógica de controle e os modos de operação básicos de leitura e escrita. A verificação funcional é uma etapa crucial para garantir o correto funcionamento do bloco  $I^2C$  controller, e serão desenvolvidos testes para verificar seu comportamento em um cenário de comunicação definido pela presença de apenas um target e a transmissão de um dado por transação no modo normal. O projeto também abordará o desenvolvimento do design digital do bloco  $I^2C$  controller que atuará nas condições já mencionadas, levando em conta a especificação feita pela NXP Semiconductors<sup>©</sup>. A verificação funcional e o design digital serão implementadas utilizando a linguagem de descrição de hardware System Veriloq. Para garantir o funcionamento do bloco, foi feita a sua síntese e a simulação do ambiente de verificação utilizando os softwares: Cadence<sup>©</sup> Xcelium Logic Simulator<sup>TM</sup>, Cadence<sup>©</sup> Genus Synthesis Solution<sup>TM</sup>, Cadence<sup>©</sup> Simvision Waveform<sup>TM</sup> e Cadence<sup>©</sup> Integrated Metrics Center<sup>TM</sup>.

**Palavras-chave:** Desenvolvimento de hardware, Microeletrônica, Verificação funcional, UVM, Design digital, Protocolo  $I^2C$ .

#### **Abstract**

This work aims to develop a digital design and functional verification of an I<sup>2</sup>C controller, a crucial component in data communication for embedded systems. The I<sup>2</sup>C protocol is widely used in the electronics industry for interconnecting integrated devices, and the controller plays the role of the main controller in this bus. The objective of this project is to design and verify an I<sup>2</sup>C controller block, considering hardware and/or software aspects such as architecture definition, communication interface, control logic, and basic read and write operation modes. Functional verification is a crucial step to ensure the correct functioning of the I<sup>2</sup>C controller block, and tests will be developed to verify its behavior in a communication scenario defined by the presence of only one target and the transmission of one data per transaction in normal mode. The project will also address the digital design development of the I<sup>2</sup>C controller block, which will operate under the mentioned conditions, taking into account the specifications provided by NXP Semiconductors<sup>©</sup>. Functional verification and digital design will be implemented using the hardware description language SystemVerilog. To ensure the block's functionality, synthesis and verification environment simulation were performed using the following software: Cadence<sup>©</sup> Xcelium Logic Simulator<sup>TM</sup>, Cadence<sup>©</sup> Genus Synthesis Solution<sup>TM</sup>, Cadence<sup>©</sup> Simvision Waveform<sup>TM</sup>, and Cadence<sup>©</sup> Integrated Metrics Center<sup>TM</sup>.

**Keywords:** Hardware development, Microelectronics, Functional verification, UVM, Digital design, I<sup>2</sup>C protocol.

# Lista de ilustrações

| Figura 1 – Fluxo de $design\ ASIC$                                                               |    |    |

|--------------------------------------------------------------------------------------------------|----|----|

| Figura 2 — Percentual do tempo do projeto de $ASIC/IC$ gasto em verificação                      |    | 7  |

| Figura 3 — Histórico de uso de Metodologias $ASIC$ e Bibliotecas de Classe Base e                | de |    |

| Testbench                                                                                        |    | Ĝ  |

| Figura 4 – Arquitetura típica de um $\mathit{Testbench}\ \mathit{UVM}\ \ldots\ldots\ldots\ldots$ |    | 10 |

| Figura 5 – Arquitetura típica de um $UVM \ Agent$                                                |    | 12 |

| Figura 6 – Condição de Início e Parada                                                           |    | 14 |

| Figura 7 – Validade do Dado                                                                      |    | 15 |

| Figura 8 – Operação de Leitura e Escrita                                                         |    | 16 |

| Figura 9 — Máquina de Estados: Controlador $I^2C$                                                |    | 19 |

| Figura 10 – Arquitetura do ambiente de verificação do controlador $I^2C$                         |    | 26 |

| Figura 11 — Simulação RTL do controlador $I^2C$                                                  |    | 29 |

| Figura 12 – Métricas de Cobertura                                                                |    | 31 |

# Lista de tabelas

| Tabela 1 - | Relatório de Área e Potência | 30 |

|------------|------------------------------|----|

| Tabela 2 - | Tabela de Testes             | 30 |

# Lista de abreviaturas e siglas

ABNT Associação Brasileira de Normas Técnicas

ASIC Application-Specific Integrated Circuit

FPGA Field-Programmable Gate Array

PDK Process Development Kit

OOP Object Orientated Programming

UVM Universal Verification Methodology

IEEE Institute of Electrical and Electronics Engineers

I<sup>2</sup>C Inter-Integrated Circuit

IP Intelectual Property

EDA Electronic Design Automation

DUT Design Under Test

TLM Transaction-Level Modeling

SDA Serial Data Line

SCL Serial Clock Line

RTL Register Transfer Level

FSM Finity State Machine

# Sumário

| 1      | INTRODUÇÃO                               | 1  |

|--------|------------------------------------------|----|

| 1.1    | Objetivos Gerais                         | 2  |

| 1.2    | Objetivos Específicos                    | 2  |

| 1.3    | Organização do Trabalho                  | 3  |

| 2      | FUNDAMENTAÇÃO TEÓRICA                    | 4  |

| 2.1    | Design de Circuitos Digitais             | 4  |

| 2.2    | Síntese Lógica                           | 5  |

| 2.3    | SystemVerilog                            | 6  |

| 2.4    | Verificação Funcional                    | 6  |

| 2.4.1  | Cobertura de Código                      | 7  |

| 2.4.2  | Cobertura Funcional                      | 8  |

| 2.5    | Universal Verification Methodology (UVM) | 8  |

| 2.5.1  | UVM Testbench                            | 10 |

| 2.5.2  | UVM Test                                 | 10 |

| 2.5.3  | UVM Environment                          | 11 |

| 2.5.4  | UVM Scoreboard                           | 11 |

| 2.5.5  | UVM Agent                                | 11 |

| 2.5.6  | UVM Sequence Item                        | 12 |

| 2.5.7  | UVM Sequence                             | 12 |

| 2.5.8  | UVM Sequencer                            | 12 |

| 2.5.9  | UVM Driver                               | 12 |

| 2.5.10 | UVM Monitor                              | 13 |

| 2.6    | Protocolo I <sup>2</sup> C               | 13 |

| 2.6.1  | Condição de Início e Parada              | 14 |

| 2.6.2  | Validade do Dado                         | 14 |

| 2.6.3  | Operação de Leitura e Escrita            | 15 |

| 3      | METODOLOGIA DE DESENVOLVIMENTO           | 17 |

| 3.1    | Design Digital                           | 17 |

| 3.1.1  | Interface                                | 17 |

| 3.1.2  | Lógica Programacional                    | 18 |

| 3.1.3  | Limitações                               | 25 |

| 3.2    | Ambiente UVM de Verificação              | 26 |

| 3.2.1  | Módulo top                               | 27 |

| 3.2.2  | Módulo <i>test</i>                       | 27 |

| 3.2.3  | Módulo <i>env</i>                                                               | 27 |

|--------|---------------------------------------------------------------------------------|----|

| 3.2.4  | Módulo scoreboard                                                               | 27 |

| 3.2.5  | Módulo subscriber                                                               | 27 |

| 3.2.6  | Módulo agent                                                                    | 28 |

| 3.2.7  | Módulo driver                                                                   | 28 |

| 3.2.8  | Módulo sequencer                                                                | 28 |

| 3.2.9  | Módulos sequence e sequence_item                                                | 28 |

| 3.2.10 | Módulo monitor                                                                  | 28 |

| 4      | RESULTADOS OBTIDOS                                                              | 29 |

| 4.1    | Simulação RTL e Síntese Lógica                                                  | 29 |

| 4.2    | Resultados e Cobertura Funcional                                                | 30 |

| 5      | CONCLUSÕES                                                                      | 32 |

|        | REFERÊNCIAS BIBLIOGRÁFICAS                                                      | 33 |

|        | ANEXO A – CÓDIGOS DO AMBIENTE DE VERIFICAÇÃO <i>UVM</i> EM <i>SYSTEMVERILOG</i> | 34 |

## 1 Introdução

O avanço tecnológico e a crescente demanda por dispositivos eletrônicos de alta performance têm impulsionado o desenvolvimento de sistemas cada vez mais complexos e integrados. Nesse contexto, a comunicação entre componentes eletrônicos se torna fundamental para o correto funcionamento desses sistemas. O barramento  $I^2C$  (Inter-Integrated Circuit) tem sido amplamente utilizado como uma solução eficiente e versátil para a interconexão de dispositivos em diversos segmentos da indústria.

Muitos periféricos populares para sistemas embarcados suportam interfaces seriais. O  $I^2C$  é um protocolo simples de curto alcance e baixa largura de banda, desenvolvido pela Philips Semiconductors<sup>©</sup> no início dos anos 1980. Atualmente, o protocolo é gerenciado e especificado pela NXP Semiconductors<sup>©</sup>, a qual faz manutenções e atualizações de forma periódica. Como pode ser visto (SEMICONDUCTOR, 2021), ele pode ter endereçamento de 7 bits ou 10 bits e utiliza duas linhas bidirecionais:  $serial\ clock\ (SCL)\ e\ serial\ data\ (SDA)$ . Todos os dispositivos na linha podem atuar como alvos ou controladores. A linha de clock é controlada apenas pelos dispositivos controladores. O envio de dados de 8 bits e endereçamento de 7 bits com bits de controle é feito em série por meio da interface. Além disso, os dispositivos controladores tem o controle, na maior parte do tempo, dos dados enviados pela linha de dados seriais, atuando como transmissor e gerenciando o início e o final da transmissão de dados. Dessa forma, tais dispositivos são essenciais para o funcionamento do protoco  $I^2C$  e do controle do fluxo de dados seriais, fazendo com que a maior parte do esforço na confecção sejam voltados para eles.

Este trabalho tem como objetivo o design digital e a verificação funcional de um bloco controlador  $I^2C$ . Serão explorados conceitos de projeto de circuitos digitais, linguagem de descrição de hardware e metodologias de verificação, com o intuito de desenvolver um bloco confiável, eficiente e compatível com os padrões e especificações do protocolo  $I^2C$ . Para que isso fosse possível, foi pensado em um cenário no qual a comunicação ocorre entre um controlador e um único alvo, com a transmissão de um único dado por transação. Como esse é o cenário básico e primordial, garantindo-se sua confiabilidade e eficiência, é possível reutilizá-lo e expandí-lo para os cenários práticos encontrado nos sistemas que utilizam múltiplos dispositivos embarcados.

O design digital foi pensado a partir das metodologias de desenvolvimento ASIC (Application-Specific Integrated Circuit) e a sua implementação foi feita utilizando a linguagem de descrição de hardware System Verilog. Já a verificação funcional do bloco foi feita a partir da metodologia UVM (Universal Verification Methodology), tendo em vista sua reusabilidade, eficiência e praticidade. Isso é possível uma vez que com o System Verilog,

foi trazida uma feature que compatibiliza o uso de OOP (Object Orientated Programming) nessa linguagem, fazendo possível o uso das classes UVM e seus recursos, tais como herança, derivação e virtualização.

Para a realização da síntese digital, foram utilizados o PDK da X-FAB® e a ferramenta de síntese da Cadence®, Genus Synthesis Solution<sup>TM</sup>.

A utilização *PDK* X-FAB® proporciona aos projetistas de ASIC a capacidade de personalizar seus circuitos de acordo com requisitos específicos, permitindo alcançar desempenho, eficiência energética e outras características desejadas. Ele encontra ampla aplicação em diversos setores, como comunicação sem fio, dispositivos de consumo, sistemas automotivos e outras áreas de alta tecnologia.

Para a simulação do *design* digital, bem como sua depuração para garantir o funcionamento correto foram utilizadas as ferramentas da Cadence<sup>®</sup>, Xcelium Logic Simulator<sup>TM</sup> e SimVision Waveform<sup>TM</sup>. Tais ferramentas são essenciais para que o código desenvolvido tenha sua confiabilidade testada.

Por fim, para a análise da cobertura de código e da cobertura funcional, foi utilizada a ferramenta da Cadence<sup>®</sup>, Integrated Metrics Center<sup>TM</sup>. Tal ferramenta permite visualizar informações essenciais para garantir que o *design* foi estimulado com as mais diversas entradas, além de gerar relatórios para análise dessas métricas.

#### 1.1 Objetivos Gerais

O objetivo geral do trabalho é propor e desenvolver um design digital de um controlador do protocolo  $I^2C$  e construir um ambiente de verificação funcional utilizando UVM para validar o funcionamento do bloco, garantindo sua confiabilidade e eficiência em um cenário de utilização básico.

#### 1.2 Objetivos Específicos

Os objetivos específicos do trabalho são listados abaixo:

- Fixar e praticar os métodos de desenvolvimento de circuitos digitais, bem como a prática da linguagem de descrição de hardware SystemVerilog

- Aprender o protocolo de comunicação  $I^2C$  e suas especificações

- Estudar os diferentes métodos existentes na metodologia *UVM* para o desenvolvimento de um ambiente de verificação funcional;

- Desenvolver um *testbench* capaz de estimular das mais diversas formas o *design* e cobrir o máximo de testes possíveis para a validação.

• Consolidar a prática no uso das ferramentas da Cadence<sup>®</sup>, bem como seus recursos e ferramentas.

#### 1.3 Organização do Trabalho

${\cal O}$ trabalho está estruturado em 5 capítulos, incluindo este introdutório, conforme a seguir.

- O Capítulo 2 apresenta a fundamentação teórica, expondo os conceitos básicos de desenvolvimento de circuitos digitais e verificação funcional, a metodologia UVM e as especificações do protocolo  $I^2C$ .

- O **Capítulo 3** aborda a metodologia utilizada para o desenvolvimento do *design* digital e do ambiente de verificação funcional, bem como suas peculiaridades e as soluções criadas para a resolução de erros e problemas.

No  ${f Capítulo~4}$  são apresentados os resultados das simulações do design digital, da síntese digital do bloco e as métricas de validação obtidas.

O Capítulo 5 apresenta as conclusões do trabalho, expondo as impressões gerais e possíveis formas de extender e melhorar o projeto.

# 2 Fundamentação Teórica

Neste capítulo, será apresentada uma fundamentação teórica sobre design de circuitos digitais, verificação funcional e UVM, e algumas especificações de funcionamento do protocolo  $I^2C$ .

#### 2.1 Design de Circuitos Digitais

O design de circuitos digitais é uma área especializada que lida com a concepção, projeto e implementação de circuitos digitais em níveis muito baixos de integração, como chips e sistemas em um único chip (SoCs). Esses circuitos digitais são essenciais para o funcionamento de dispositivos eletrônicos modernos, como computadores, smartphones, sistemas embarcados e muito mais. Eles envolvem a integração de componentes eletrônicos, como transistores, resistores, capacitores, entre outros, em um único chip.

Ao projetar circuitos digitais para microeletrônica, alguns dos principais desafios incluem o aumento da densidade de integração, a redução do consumo de energia, o aumento da velocidade de operação e a garantia de confiabilidade e robustez.

Uma das áreas de desenvolvimento de circuitos digitais mais abrangentes nos dias atuais é a área de design ASIC. É uma área especializada e que se concentra na criação de chips personalizados para aplicações específicas. Diferentemente dos chips de propósito geral, como microprocessadores, ASICs são projetados para executar tarefas específicas e são otimizados para desempenho, consumo de energia e custo.

O processo de design ASIC envolve várias etapas, como a definição dos requisitos do circuito, a criação da especificação de design, a implementação do circuito em um nível de abstração de alto nível, a simulação e verificação, a síntese lógica, o layout físico, a verificação pós-layout e a fabricação do chip, como pode ser visto em (MARTIN, 2002).

Chip Design Specification 2 Architectural Design 3 Behavioral & Functional modelling

Synthesis & 5 Logical implementation 4

6 PNR 7 Design Layout

Figura 1 – Fluxo de design ASIC

Fonte: (CHAUHAN, 2020).

#### 2.2 Síntese Lógica

A síntese lógica de *hardware* desempenha um papel essencial no desenvolvimento de circuitos integrados. Ela consiste em converter uma descrição de alto nível de um circuito digital em uma representação de baixo nível adequada para a implementação em um chip. O principal objetivo da síntese lógica é otimizar o *design* em termos de área ocupada, consumo de potência e desempenho, garantindo que o circuito funcione corretamente (HOLLINGWORTH, 1990).

Durante o processo de síntese, várias etapas são executadas. Inicialmente, ocorre o mapeamento de portas lógicas, em que as descrições de alto nível, como RTL, são transformadas em uma representação utilizando uma biblioteca de células lógicas padrão. Essas células lógicas representam as operações básicas, como portas AND, OR e NOT, que são implementadas usando transistores. Em seguida, é realizada a otimização de nível e tecnologia, na qual são aplicadas técnicas para melhorar o desempenho do circuito em termos de área, potência e velocidade. Isso envolve a substituição de células lógicas por outras mais eficientes e a reorganização do circuito para reduzir a área ocupada e minimizar as conexões entre os elementos. Por fim, é feita a alocação de recursos, que determina como os elementos físicos, como transistores e interconexões, serão posicionados no chip. Nessa etapa, são considerados fatores como a localização dos elementos e a minimização do atraso de propagação entre eles.

No mercado, existem diversas ferramentas de síntese lógica disponíveis, que suportam diferentes níveis de abstração e oferecem recursos avançados para otimização do design. Essas ferramentas desempenham um papel crucial no desenvolvimento de circuitos integrados eficientes e funcionais, permitindo que os projetistas aproveitem ao máximo os

recursos disponíveis.

#### 2.3 SystemVerilog

A linguagem de descrição de hardware System Verilog desempenha um papel fundamental no projeto de circuitos digitais, fornecendo uma linguagem de alto nível para modelagem e simulação do comportamento de sistemas digitais complexos (SUTHER-LAND; DAVIDMANN; FLAKE, 2006). É uma extensão poderosa do Verilog, contendo recursos adicionais que aprimoram a capacidade de descrever, simular e verificar projetos de hardware.

Uma das principais vantagens do System Verilog é sua capacidade de descrever circuitos digitais em diferentes níveis de abstração. Ele suporta descrições estruturais, onde os componentes do circuito são conectados por portas e sinais, e descrições comportamentais, onde o comportamento do circuito é especificado usando regras e equações. Essa flexibilidade permite que os projetistas escolham o nível de detalhe que melhor se adapta à tarefa em questão. Uma característica importante do System Verilog é a digitação de dados. Tipos de dados poderosos, como números inteiros, reais, vetores e estruturas definidas pelo usuário, são introduzidos para tornar a modelagem de circuitos mais precisa e robusta. Além disso, a linguagem suporta primitivas de concorrência que permitem a escrita de circuitos assíncronos e paralelos que podem executar múltiplas operações simultaneamente.

Outro aspecto importante do *SystemVerilog* é a verificação do projeto. Ele fornece recursos poderosos para criar asserções (VIJAYARAGHAVAN; RAMANATHAN, 2005), que são instruções lógicas para testar propriedades específicas do circuito. Isso ajuda os *designers* a encontrar erros e garantir que o design esteja correto. Além disso, o *SystemVerilog* oferece suporte à verificação formal, uma técnica avançada que permite a verificação automática das propriedades do projeto sem simulação, contribuindo para uma verificação mais abrangente e eficiente.

O System<br/>Verilog é especificado e mantido pela *IEEE* através do padrão *IEEE Std*<br/>1800. O padrão define a linguagem, incluindo sua sintaxe, semântica e recursos.

#### 2.4 Verificação Funcional

A verificação funcional é uma etapa essencial no desenvolvimento de circuitos digitais, que visa garantir a equivalência entre as especificações definidas e a implementação em RTL. Com a crescente complexidade dos blocos ASIC modernos, tornou-se inviável realizar testes exaustivos, exigindo estratégias mais eficazes para cobrir o maior número possível de casos de teste, considerando as restrições de tempo e recursos.

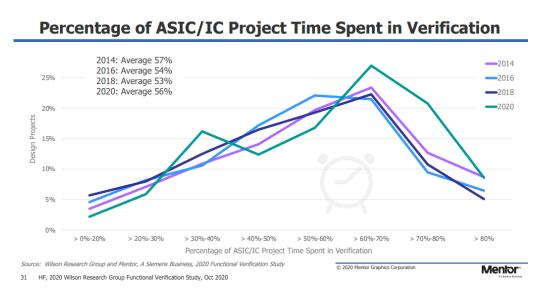

A verificação representa cerca de 70% do esforço total de design, sendo uma etapa crucial no processo de desenvolvimento (KUMAR; GOPINATH, 2016). Ela está no caminho crítico do projeto, demandando tempo significativo. No entanto, é possível reduzir o tempo de verificação por meio da utilização de abstração e uso de IP e designs pré-verificados. A abstração na verificação permite simplificar o processo, reduzindo o foco em detalhes de baixo nível. Embora isso possa resultar em menos controle sobre esses detalhes, é uma estratégia eficaz para agilizar a verificação. A Figura 2 ilustra o tempo gasto na verificação em relação ao tempo total do desenvolvimento de um projeto ASIC.

Figura 2 – Percentual do tempo do projeto de ASIC/IC gasto em verificação.

Fonte: (FOSTER, 2020).

Além disso, a automação é uma ferramenta essencial para a redução do tempo de verificação. Ao automatizar tarefas repetitivas, é possível acelerar o processo e aumentar a eficiência. A aleatorização também pode ser utilizada como uma ferramenta de automação na verificação. Ao gerar estímulos de teste de forma aleatória, é possível explorar uma ampla gama de cenários de uso e identificar potenciais problemas de forma mais eficiente.

As principais métricas da verificação funcional são as coberturas de código e funcional. Elas permitem identificar o quão abrangente são os estímulos gerados pelo ambiente de verificação em comparação com as possibilidades existentes, a partir do tamanho em *bits* das variáveis.

#### 2.4.1 Cobertura de Código

A cobertura de código é uma métrica que avalia o quanto o código do design foi testado usando o banco de testes. Ela mede a extensão em que diferentes partes do código

foram exercitadas, incluindo expressões, alternância de pinos e máquinas de estados finitos (FATHY; SALAH; GUINDI, 2015). No entanto, é importante destacar que a cobertura de código não fornece informações sobre se o design foi testado de acordo com sua intenção original.

Embora seja uma ferramenta útil para avaliar a abrangência dos testes, ela não garante que todos os possíveis caminhos e comportamentos do design tenham sido exercitados. Para uma avaliação mais abrangente, é necessário complementar a cobertura de código com a cobertura funcional, que verifica se as funcionalidades e requisitos específicos do design foram adequadamente testados.

A cobertura de código é geralmente gerada automaticamente pela ferramenta de verificação utilizada, permitindo identificar quais partes do código foram executadas durante os testes. Essa métrica auxilia os engenheiros de verificação a identificar lacunas nos testes e a direcionar esforços para garantir uma cobertura mais completa do design.

#### 2.4.2 Cobertura Funcional

A cobertura funcional é uma medida que analisa se o design está em conformidade com sua especificação funcional e identifica possíveis desvios em relação a essa especificação. O uso das palavras-chaves cover, covergroups, bins e cross permitem verificar se determinadas condições ou funcionalidades estão sendo adequadamente exercitadas durante os testes(SALAH, 2014).

A cobertura funcional vai além da simples execução do código, pois envolve uma análise mais profunda das funcionalidades do design e sua correspondência com a especificação. Ela ajuda a garantir que todas as principais funcionalidades do design sejam testadas e fornece informações valiosas sobre a integridade e conformidade do sistema.

Ao estabelecer metas de cobertura funcional, os engenheiros de verificação definem os critérios para avaliar se o design está atendendo às expectativas e requisitos funcionais estabelecidos. Essa abordagem é fundamental para garantir que o design esteja corretamente implementado e que as funcionalidades importantes estejam sendo testadas de maneira adequada.

#### 2.5 Universal Verification Methodology (UVM)

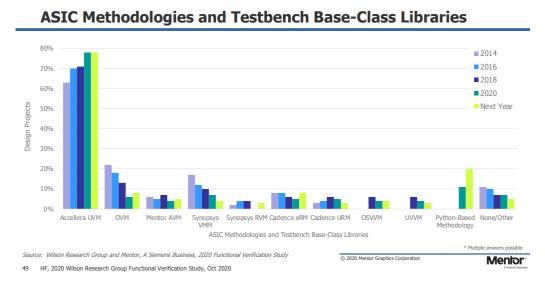

A *UVM* é uma metodologia amplamente adotada para a verificação funcional de hardware. Baseada em orientação a objetos e utilizando a linguagem *SystemVerilog*, ela oferece uma estrutura reutilizável para criar ambientes de verificação eficientes. Com sua portabilidade, a *UVM* pode ser utilizada com diversas ferramentas de *EDA*, permitindo a reutilização do ambiente de verificação em diferentes plataformas de simulação. Foi

desenvolvida pela Accellera Systems Initiative<sup>®</sup> e incentiva a reutilização de *testbenches* e componentes de verificação, facilitando a criação de casos de teste e o desenvolvimento de modelos transacionais para melhorar a eficiência do processo de verificação.

Figura 3 – Histórico de uso de Metodologias ASIC e Bibliotecas de Classe Base de Testbench

Fonte: (FOSTER, 2020)

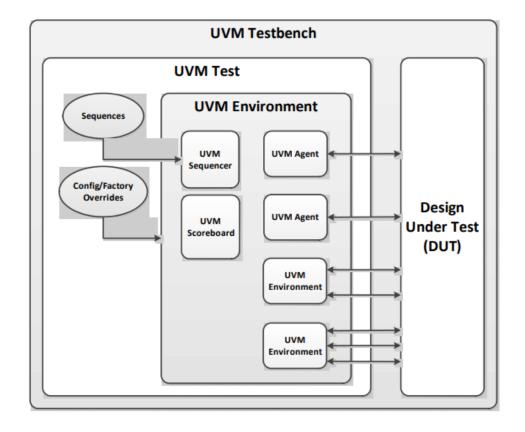

A metodologia *UVM* segue uma arquitetura típica para a concepção de *testbenches*. A Figura 4 ilustra a hierarquia da arquitetura e seus componentes. Logo após, serão definidos os componentes dessa arquiteturas especificados em (INITIATIVE, 2015).

Figura 4 – Arquitetura típica de um Testbench UVM

Fonte: (INITIATIVE, 2015)

#### 2.5.1 UVM Testbench

A arquitetura típica do *UVM Testbench*, também conhecido como módulo *top*, envolve a instanciação do módulo *DUT* e da classe de teste *UVM Test*, além da configuração das conexões entre eles. Se os elementos de verificação incluírem componentes baseados em módulos, eles também são instanciados sob o *UVM Testbench*. O *UVM Test* é instanciado dinamicamente em tempo de execução, permitindo que o *UVM Testbench* seja compilado uma vez e executado com vários testes diferentes.

#### 2.5.2 UVM Test

O  $UVM\ Test$  é o componente de nível superior no  $UVM\ Testbench$ . Sua função principal é realizar três atividades: instanciar o ambiente de nível superior, configurar o ambiente (por meio de substituições de fábrica ou do banco de dados de configuração) e aplicar estímulos invocando Sequências UVM através do ambiente para o DUT.

Geralmente, há um UVM Test base que contém a instanciação do ambiente UVM e outros elementos comuns. Em seguida, outros testes individuais estendem esse teste base

e podem configurar o ambiente de forma diferente ou selecionar sequências diferentes para executar.

#### 2.5.3 UVM Environment

Um *UVM Environment* abrange os componentes *agents* e *scoreboards* e, frequentemente, outros ambientes em sua hierarquia. Ele reúne diversos componentes críticos do *testbench*, permitindo que sejam configurados facilmente em um único local, se necessário, em qualquer estágio. Pode ter vários *agents* para diferentes interfaces e múltiplos *scoreboards* para verificar diferentes tipos de transações de dados. Dessa forma, o ambiente permite habilitar ou desabilitar diferentes componentes de verificação para tarefas específicas em um único local.

#### 2.5.4 UVM Scoreboard

A função principal do *UVM Scoreboard* é verificar o comportamento de um determinado DUT. O *UVM Scoreboard* geralmente recebe transações contendo as entradas e saídas do DUT por meio das portas de análise do *UVM Agent*. Ele executa as transações de entrada por meio de um modelo de referência (também conhecido como preditor) para produzir transações esperadas e, em seguida, compara as saídas esperadas com as saídas reais. Existem diferentes metodologias para implementar o *scoreboard*, variando na natureza do modelo de referência e na forma de comunicação entre o *scoreboard* e o restante do *testbench*.

#### 2.5.5 UVM Agent

Um UVM Agent consiste em um agrupamento dos componentes sequenciador,  $driver\ e\ monitor$  de uma interface. Pode-se utilizar vários agentes para controlar múltiplas interfaces, e todos eles são conectados ao testbench por meio do componente de ambiente. Existem agentes ativos e passivos. Os agentes ativos possuem um driver e têm a capacidade de controlar sinais, enquanto os agentes passivos possuem apenas o monitor e não podem controlar os pinos. Mesmo que um agente passivo seja composto apenas pelo monitor, é importante manter o nível de abstração prometido pelo UVM e preservar sua estrutura, colocando todos os agentes no ambiente em vez de subcomponentes isolados, como monitores. Por padrão, um agente é considerado ativo, mas isso pode ser alterado usando o método set() do banco de dados de configuração UVM. A Figura 5 ilustra a arquitetura típica de um UVM Agent.

UVM Agent

UVM Driver

BUT

Interface

Figura 5 – Arquitetura típica de um UVM Agent

Fonte: (INITIATIVE, 2015)

#### 2.5.6 UVM Sequence Item

Um *UVM Sequence Item* é o elemento fundamental da arquitetura *UVM*. É uma transação que contém dados, métodos e possivelmente restrições associadas ao *DUT*. O *UVM Sequence Item* representa a menor unidade transacional que pode ocorrer em um ambiente de verificação.

#### 2.5.7 UVM Sequence

Um *UVM Sequence* é um conjunto de transações. Uma sequência possibilita a capacidade de usar a transação conforme os requisitos e utilizar quantas transações quiser. A principal função de uma sequência é gerar transações e enviá-las para o sequenciador.

#### 2.5.8 UVM Sequencer

Um UVM Sequencer desempenha o papel de intermediário entre as transações e o driver, controlando o fluxo de transações provenientes de várias sequências. Uma interface TLM possibilita a comunicação entre o driver e o sequenciador.

#### 2.5.9 UVM Driver

Um UVM Driver converte as transações recebidas do sequenciador em atividades de nível de sinal no DUT. Para realizar essa conversão, são utilizados métodos como

get\_next\_item(), try\_next\_item(), item\_done() e put(). O UVM Driver é, geralmente, uma classe parametrizada com o tipo de transação utilizada por ela.

#### 2.5.10 UVM Monitor

O *UVM Monitor* monitora a atividade em nível de sinal do DUT e a converte em transações para serem enviadas a outros componentes para análise adicional. Normalmente, o monitor processa as transações, como coleta de cobertura e registro, antes de enviá-las aos *scoreboards*.

#### 2.6 Protocolo *I*<sup>2</sup>*C*

O protocolo de comunicação serial  $I^2C$  é uma solução amplamente empregada para a comunicação entre dispositivos eletrônicos em uma variedade de aplicações. Desenvolvido pela Philips® (atualmente NXP Semiconductors®), o  $I^2C$  oferece um meio eficiente e de fácil implementação para a troca de dados entre diferentes componentes de um sistema. O  $I^2C$  é baseado em um barramento serial de dois fios, composto por uma linha de dados (SDA) e uma linha de clock (SCL). Essas linhas são compartilhadas por todos os dispositivos conectados ao barramento, com cada dispositivo possuindo um endereço único que possibilita sua identificação durante as comunicações.

O protocolo  $I^2C$  suporta dois modos de operação: controlador e alvo. O dispositivo controlador é responsável por iniciar e controlar as transmissões, enquanto os dispositivos alvos respondem aos comandos enviados pelo controlador. O controlador também gerencia o acesso ao barramento, evitando colisões e garantindo uma comunicação adequada. A comunicação  $I^2C$  ocorre por meio de quadros de bytes, chamados de quadros  $I^2C$ , que contêm um endereço de destino, identificando o dispositivo de destino, juntamente com os dados a serem transmitidos. O protocolo  $I^2C$  também oferece recursos como repetição de início (start) e término (stop), permitindo a comunicação contínua entre dispositivos.

Uma das principais vantagens do protocolo  $I^2C$  é sua simplicidade e baixo consumo de recursos. Ele possibilita a conexão de vários dispositivos em um único barramento, facilitando a integração de componentes em um sistema. Além disso, o  $I^2C$  permite a configuração da velocidade de comunicação, tornando-a ajustável conforme as necessidades do projeto. O protocolo  $I^2C$  é amplamente adotado em diversas aplicações, incluindo comunicação entre sensores e microcontroladores, controle de periféricos e memórias, entre outros. É uma solução confiável, amplamente suportada pelos fabricantes e amplamente utilizada na indústria eletrônica.

O protocolo possui diversos recursos mostrados em (SEMICONDUCTOR, 2021). No entanto, serão abordados apenas os seguintes recursos:

- Condição de início e parada (Start and stop condition)

- Operações de leitura e escrita

- Reconhecimento (acknowledgement) e validade do dado serial

#### 2.6.1 Condição de Início e Parada

Como descrito em (KAITH; PATEL; GUPTA, 2015), toda transmissão de dados via protocolo  $I^2C$  inicia-se a partir de uma condição de início e se encerra por meio de uma condição de parada, ambas caracterizadas pelos sinais do barramento SDA e SCL. A condição de início é feita pelo controlador ao proporcionar uma transição de nível lógico alto (1) para o nível lógico baixo (0) em SDA, enquanto que SCL é mantido em nível lógico alto (1). Já a condição de parada acontece quando há um transição de nível lógico baixo (0) para o nível lógico alto (1) em SDA, enquanto que SCL é mantido em nível lógico alto (1).

SDA

SCL

START condition

STOP condition

Figura 6 - Condição de Início e Parada

Fonte: (SEMICONDUCTOR, 2021)

#### 2.6.2 Validade do Dado

A validade do dado serial na linha SDA, segundo (KAITH; PATEL; GUPTA, 2015), ocorre quando a linha SCL está em nível lógico baixo (0). Portanto, nesse momento, é possível que os alvos e controladores obtenham dados válidos em SDA para escrita ou leitura. Já quando a linha SCL está em nível lógico alto (1), é permitida a troca de dados na linha SDA.

SCL data line change stable; of data allowed

Figura 7 – Validade do Dado

Fonte: (SEMICONDUCTOR, 2021)

#### 2.6.3 Operação de Leitura e Escrita

Durante uma operação de escrita no  $I^2C$ , o dispositivo controlador inicia a transmissão enviando um quadro  $I^2C$  contendo o endereço do dispositivo alvo e os dados a serem escritos. O dispositivo alvo correspondente reconhece seu endereço enviando um bit de reconhecimento (em nível lógico alto) e recebe os dados, realizando a ação apropriada com base nas informações recebidas.

Por outro lado, na operação de leitura, o dispositivo controlador inicia a transmissão enviando um quadro  $I^2C$  com o endereço do dispositivo alvo e um bit indicando que uma leitura será realizada. O dispositivo alvo correspondente reconhece o endereço e prepara os dados para serem enviados de volta ao dispositivo controlador. Em seguida, o dispositivo controlador recebe os dados enviados pelo dispositivo alvo e manda um bit de reconhecimento (1 para ler o próximo dado e 0 para encerrar a transmissão).

No contexto de um sistema eletrônico, as operações de leitura e escrita no protocolo  $I^2C$  são controladas pelo dispositivo controlador, que coordena a comunicação, envia os comandos e recebe as respostas dos dispositivos alvos. É crucial que os dispositivos estejam configurados corretamente com os endereços apropriados e que as sequências de escrita e leitura sejam seguidas corretamente para garantir uma comunicação eficaz entre os dispositivos. A flexibilidade bidirecional do protocolo  $I^2C$ , que permite a troca de dados em ambos os sentidos, torna-o amplamente utilizado em uma variedade de aplicações eletrônicas. Ele oferece uma solução confiável e eficiente para a comunicação entre dispositivos, permitindo a integração efetiva de componentes em sistemas eletrônicos complexos.

1 R/W SLAVE ADDRESS DATA DATA S data transferred (n bytes + acknowledge) (read) A/Ā SLAVE ADDRESS R/W DATA S DATA Α data transferred '0' (write) (n bytes + acknowledge) from master to slave A = acknowledge (SDA LOW) A = not acknowledge (SDA HIGH) from slave to master S = START condition P = STOP condition

Figura 8 – Operação de Leitura e Escrita

Fonte: (SEMICONDUCTOR, 2021)

## 3 Metodologia de Desenvolvimento

Esse capítulo discute acerca da metodologia utilizada para o desenvolvimento do design digital do controlador  $I^2C$ , bem como suas características e limitações. Além disso, trata também sobre o ambiente de verificação funcional, suas características e componentes, e sua arquitetura geral.

#### 3.1 Design Digital

O design do controlador  $I^2C$  foi pensado de acordo com as especificações do protocolo mencionadas na Seção 2.6. O enlace de comunicação proposto é de cárater básico e essencial, dado por:

- Comunicação entre apenas um controlador e um alvo.

- Transmissão de um único dado por vez (seja de leitura ou escrita).

- O alvo possui endereço único e, portanto, seu reconhecimento é sempre positivo à chamada do controlador no barramento.

- O controlador é isento do tratamento do n\(\tilde{a}\) reconhecimento de um dado, apenas reportando a falha.

Apesar de ser um enlace simples, ele tem um caráter fundamental no funcionamento correto da comunicação dos dispositivos. Tendo isso como ponto de partida, é totalmente viável expandir os recursos do controlador e fazer testes mais robustos com a presença de mais alvos no barramento.

Diante disso, faz-se necessário uma descrição da lógica programacional utilizada para conceber o controlador  $I^2C$ , bem como suas características funcionais e limitações, visto que o protocolo  $I^2C$  completo possui mais recursos que serão abordados no tópico.

#### 3.1.1 Interface

O controlador  $I^2C$  projetado foi pensado com o foco no controle do barramento serial e nas operações do protocolo. A geração dos sinais que executam esse controle foi abstraída, uma vez que a verificação será feita segundo o escopo do protocolo  $I^2C$ . Dessa forma, esses sinais foram colocados como entradas do bloco, facilitando a geração de estímulos e simplificando a lógica do algoritmo. O controlador possui a seguinte interface de entrada:

```

interface i2c_interface (input bit clk, input bit reset);

2

3

// Inputs

logic start;

4

5

logic stop;

6

logic rw;

logic [6:0] addr;

7

logic [7:0] w_data;

8

9

// Outputs

10

logic i2c_scl;

11

logic i2c_sda;

12

13

14

modport master(input clk, reset, start, stop, rw, addr, w_data,

15

output i2c_scl, inout i2c_sda);

16

scl, inout sda, input clk, input rst);

// modport mst(input

endinterface

```

Fonte: Autoria própria.

Os sinais start e stop são os responsáveis pela sinalização ao controlador que deve ser iniciada/finalizada uma transmissão de dados. A partir deles, o controlador executa a condição de início/parada no barramento, especificada na Seção 2.6.1. O sinal rw indica ao controlador a operação que deverá ser feita na transmissão, seja ela escrita ou leitura. O valor desse sinal será enviado ao barramento logo após a finalização do envio do endereço.

O sinal addr contém o valor do endereço de 7 bits (o protocolo permite endereços de 7 ou de 10 bits, nesse caso foi escolhido um enlace com endereços de 7 bits). Ele é enviado de forma serial pelo barramento. Já o sinal  $w\_addr$  contém o dado a ser escrito, caso a operação seja de escrita.

Os sinais  $i2c\_scl$  e  $i2c\_sda$  são os sinais SCL e SDA do barramento. Note que SDA é definido como inout uma vez que pode servir de entrada ou saída para o controlador, devido a bi-direcionalidade do barramento.

#### 3.1.2 Lógica Programacional

Para descrever a lógica de funcionamento e o controle dos sinais transmitidos pra a linha SDA, foi utilizada uma máquina de estados, ilustrada pela Figura 9:

start = 0 STATE\_IDLE start = 1STATE\_START STATE\_ADDR STATE\_RW STATE\_ACK rw = 0rw = 1STATE\_WDATA STATE\_RDATA STATE\_ACKW STATE\_ACKR STATE\_STOP

Figura 9 – Máquina de Estados: Controlador  $I^2C$

Fonte: Autoria própria.

Cada estado define uma etapa do envio de dados em uma transmissão pelo barramento serial. Com a lógica de máquina de estados, torna-se mais fácil definir a saída SDA e obter os dados quando ela é uma entrada do bloco. Para utilizar  $i2c\_sda$  como uma variável inout, foi usado um  $buffer\ tri-state$  com o sinal de controle io, que permite identificar quando é saída e quando é entrada.

O código abaixo mostra o design completo, com as lógicas de cada estado:

```

`include "uvm_macros.svh"

`include "i2c_pkg.svh"

`include "i2c interface.svh"

5 module i2c_master (i2c_interface.master vif);

typedef enum logic [3:0]

8

//00

STATE_IDLE,

9

STATE_START,

//01

STATE_ADDR,

//02

11

STATE_RW,

//03

12

STATE_ACK,

//04

13

STATE_WDATA,

//05

14

STATE_RDATA,

15

STATE_ACK_WDATA, //06

16

STATE ACK RDATA,

17

STATE_STOP

//07

18

} state;

19

20

state current, next;

21

22

always_ff @(posedge vif.clk or posedge vif.reset) begin

23

24

if (vif.reset) begin

current < STATE_IDLE;</pre>

25

end else begin

26

current ≤ next;

27

28

end

end

29

30

logic [7:0] count;

31

logic i2c_scl_enable;

32

logic [6:0] saved_addr;

34

logic [7:0] r_data;

35

logic ack_addr;

36

logic ack_data;

37

38

logic [7:0] saved_wdata;

```

```

39

40

// criar variavel io para definir a dire o de i2c_sda

41

logic io; // in (io = 0); out (io = 1);

42

logic sda;

43

44

logic sda_enable;

45

assign vif.i2c\_scl = (i2c\_scl\_enable == 0) ? 1 : \neg vif.clk;

46

assign vif.i2c_sda = (sda_enable) ? sda : 'bz;

48

49

50

always_comb begin

51

if (vif.reset == 1) begin

52

i2c\_scl\_enable = 0;

53

54

end

else begin

55

if ((current == STATE_IDLE) || (current == STATE_START) || (...

56

current == STATE_STOP)) begin

i2c\_scl\_enable = 0;

57

58

end

else begin

59

i2c\_scl\_enable = 1;

60

61

end

end

62

end

63

64

65

always_ff @(posedge vif.clk) begin

66

67

case (current)

68

STATE_IDLE: begin

69

if(vif.start) begin

70

next \leq STATE\_START;

71

72

//io \leq 1;

73

end

else next \le STATE_IDLE;

75

76

end

78

STATE_START: begin

79

next \le STATE\_ADDR;

80

count \leq 6;

81

//io \leq 1;

82

83

84

```

```

85

STATE_ADDR: begin

86

if (count == 1) begin

87

next < STATE_RW;

88

//io \leq 1;

89

90

end

91

if (count != 0) begin

92

count \leq count - 1;

93

end

94

95

end

96

97

STATE_RW: begin

98

next \leq STATE\_ACK;

99

//io \leq 1;

100

101

end

102

103

104

STATE_ACK: begin

105

if (! vif.rw) next < STATE_WDATA;</pre>

106

else next < STATE_RDATA;</pre>

108

count \leq 7;

//io \leq 0;

109

110

111

end

112

STATE_WDATA: begin

113

114

if (count == 1) begin

115

next \leq STATE\_ACK\_WDATA;

end

116

117

if (count != 0) begin

118

count < count - 1;

119

120

end

121

end

122

123

STATE_RDATA: begin

124

if (count == 1) begin

125

next \le STATE\_ACK\_RDATA;

126

end

127

128

if (count != 0) begin

129

count \leq count - 1;

130

131

```

```

132

end

133

STATE_ACK_WDATA: begin

134

if(vif.stop) next < STATE_STOP;</pre>

135

//io \leq 0;

136

137

end

138

STATE_ACK_RDATA: begin

139

next \leq STATE\_STOP;

140

end

141

142

STATE_STOP: begin

143

next < STATE_IDLE;

144

//io \leq 1;

145

146

end

147

endcase

148

end

149

150

always_comb begin

151

case (current)

152

STATE_IDLE: begin

153

sda_enable = 1;

154

io = 1;

155

if(io) sda = 1;

156

else

sda = sda;

157

end

158

159

STATE_START: begin

160

161

io = 1;

162

sda_enable = 1;

saved_addr = vif.addr;

163

saved_wdata = vif.w_data;

164

if(io) sda = 0;

165

else sda = sda;

166

167

168

end

169

STATE_ADDR: begin

170

io = 1;

171

172

sda_enable = 1;

if(io) sda = vif.addr[count];

173

else sda = sda;

174

175

176

end

177

STATE_RW: begin

178

```

```

io = 1;

179

sda_enable = 1;

180

if (io) sda = vif.rw;

181

else sda = sda;

182

183

184

end

185

STATE_ACK: begin

186

io = 0;

sda_enable = 1;

188

if (!io) begin

189

ack\_addr = vif.i2c\_sda;

190

sda = vif.i2c\_sda;

191

end

192

193

else begin

194

sda = sda;

195

end

196

197

end

198

199

STATE_WDATA: begin

200

io = 1;

sda_enable = 1;

202

203

if(io) sda = vif.w_data[count];

204

205

else sda = sda;

206

end

207

208

209

STATE_RDATA: begin

io = 0;

210

sda_enable = 1;

211

212

if (!io) begin r_data[count] = vif.i2c_sda;

213

sda = vif.i2c\_sda;

214

215

\quad \text{end} \quad

else sda = sda;

216

end

217

218

STATE_ACK_WDATA: begin

219

io = 0;

220

sda_enable = 1;

221

if (!io) begin

222

ack_data = vif.i2c_sda;

223

sda = vif.i2c\_sda;

224

225

```

```

226

else begin

227

sda = sda;

228

end

229

230

231

end

232

STATE_ACK_RDATA: begin

233

io = 1;

234

sda_enable = 1;

235

236

if(io) sda = 1;

237

else sda = sda;

238

end

239

240

STATE_STOP: begin

241

io = 1;

242

sda_enable = 1;

243

if(io) sda = 1;

244

else sda = sda;

245

246

end

247

default: sda = 0;

249

endcase

250

251

end

252

253

254

255 endmodule

```

Fonte: Autoria própria.

## 3.1.3 Limitações

As principais limitações do design digital referem-se a sua simplicidade e são listadas abaixo:

- Transmissão de um dado por vez no barramento serial.

- Não há tratamento do não reconhecimento de uma operação.

- Não é otimizado para um transmissão ideal de um único byte com todas as informações, uma vez que não possui um gerador de frequência pra linha *SCL*.

- Não apresenta mais de um modo de funcionamento, apenas o modo normal sincronizado com o *clock* do bloco controlador.

- Não tem definição para arbitrar em um barramento com mais de um alvo.

Essas limitações reiteram o caráter básico e essencial do bloco projetado e abrem novos horizontes para a continuidade da pesquisa, a partir da implementação das mais diversas funcionalidades descritas em (SEMICONDUCTOR, 2021).

## 3.2 Ambiente UVM de Verificação

O ambiente de verificação funcional feito para testar o controlador  $I^2C$  foi pensado a partir da metodologia UVM. Cada componente utilizado faz parte da arquitetura geral do ambiente, que foi ilustrada pela Figura 10. Os códigos referentes a cada componente está disposto na seção Apêndice A.

my\_test

my\_env

i2c\_scoreboard

i2c\_agent

i2c\_sequence\_item

i2c\_sequence\_ttem

i2c\_interface

input\_signs

output\_signs

Figura 10 – Arquitetura do ambiente de verificação do controlador  $I^2C$

Fonte: Autoria própria.

## 3.2.1 Módulo top

O módulo top é o componente mais externo da arquitetura. Nele são instanciados os módulos de interface e o DUT, também é gerado o clock e os pacotes são incluídos, para que ele tenha acesso a todos os componentes do ambiente.

#### 3.2.2 Módulo test

No módulo test são instanciados os objetos environment e sequence e também é dado início a sequência de transações enviadas para estimular o DUT.

## 3.2.3 Módulo env

No módulo environment são instanciados os componentes agent, scoreboard e subscriber. Também é onde são conectadas as portas de análise, por onde são enviadas as transações para a checagem do funcionamento do DUT.

## 3.2.4 Módulo scoreboard

No módulo scoreboard são feitas as checagens do funcionamento do DUT. Foram feitos três testes para cobrir o funcionamento do controlador  $I^2C$ :

- Teste de condição de início: checa se os valores da linha serial *SDA* no momento de iniciar a transmissão condizem com o especificado na Figura 6.

- Teste de operação de leitura/escrita: checa se os valores recuperados a partir da linha serial SDA condizem com os valores aleatórios gerados como entrada do DUT.

No caso da leitura, checa se o valor de SDA é 0 ao final da leitura, uma vez que esse valor simboliza o reconhecimento e o término da transmissão do dado.

- Teste de condição de parada: Teste de condição de parada: checa se os valores da linha serial SDA no momento de finalizar a transmissão condizem com o especificado na Figura 6.

Além disso, são gerados arquivos .txt que contém a quantidade de acertos (matches) e erros (mismatches), podendo inferir a confiabilidade do design ao juntar com as métricas de cobertura funcional.

#### 3.2.5 Módulo subscriber

No módulo subscriber são criados os coverpoints para medir a quantidade de valores cobertos no estímulo do DUT. Cada um dos coverpoints geram bins que são contadores

responsáveis por aumentar cada vez que o valor que eles representam for gerado. É utilizada a função cq sample() para a amostragem dos bins.

## 3.2.6 Módulo agent

No módulo agent são instanciados os componentes driver, sequencer e monitor. É criada uma porta de análise derivada da transação que é conectada ao monitor e, por meio dela, são enviadas as transações recuperadas da interface para o scoreboard. Além disso, o sequencer é conectado ao driver e passa a enviar as sequências de transações para ele.

#### 3.2.7 Módulo driver

No módulo driver são criados uma interface virtual e uma transação. A partir disso são feitas duas tarefas que estimulam o DUT: reset\_phase() e main\_phase(). Na primeira delas, é feito o reset das variáveis da interface. Já na outra, tarefas auxiliares são utilizadas para estimular a interface com valores aleatórios. Uma analogia válida para esse caso é que o driver funciona como um alvo funcionaria: estimulando o barramento com respostas às ações do controlador e enviando dados quando necessário.

## 3.2.8 Módulo sequencer

O módulo sequencer é responsável por gerar as sequências de transações e enviá-las para o driver.

## 3.2.9 Módulos sequence e sequence\_item

O módulo  $sequence\_item$  contém as variáveis responsáveis por estimular e coletar o comportamento do DUT. Ja o módulo sequence é responsável por iniciar a transação e randomizá-la.

#### 3.2.10 Módulo monitor

O módulo *monitor* tem um papel contrário ao do *driver*. Ele faz o uso de tarefas para coletar os valores da interface e enviá-los para os módulos que executam a checagem do funcionamento.

Uma necessidade primordial para o monitor é a sincronização com as operações do DUT, para que os sinais recuperados sejam correspondentes às operações a serem checadas. Para isso faz-se uso de controle de eventos temporais, um dos recursos da linguagem SystemVerilog.

## 4 Resultados Obtidos

Neste capítulo, serão mostrados e analisados os resultados da simulação RTL, a síntese lógica do design, o resultado das comparações do scoreboard e as métricas de cobertura funcional.

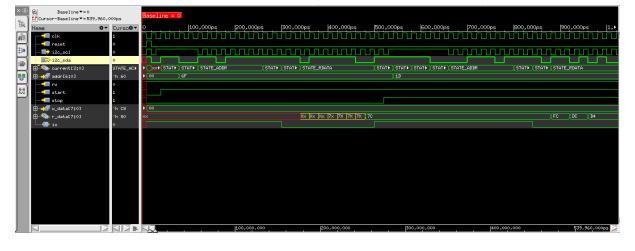

## 4.1 Simulação RTL e Síntese Lógica

Para realizar a simulação RTL foi utilizada a ferramenta da Cadence<sup>©</sup> Xcelium Logic Simulator<sup>TM</sup> e para o debug do funcionamento por meio das formas de onda foi utilizada a ferramenta SimVision Waveform<sup>TM</sup>. Como pode ser visto na Figura 11, a simulação ocorreu sem erros e seu funcionamento ocorre de acordo com o especificado em (SEMICONDUCTOR, 2021). É possível visualizar também o pequeno atraso para a mudança de alguns estados da FSM contruída, resultando no problema de sincronismo mencionado na Seção 3.2.10. Isso pode ser resolvido a partir do uso de um gerador de frequência pra linha SCL permitindo um maior controle sobre a frequência dos dados no barramento.

Figura 11 – Simulação RTL do controlador I<sup>2</sup>C

Fonte: Autoria própria.

Já para a síntese lógica do bloco, foi utilizada a ferramenta Genus Synthesis Solution  $^{\rm TM}$  e o PDK de 180nm da XFAB . Tanto para a simulação , quanto para a síntese lógica foi utilizado o período de clock utilizado foi 20ns. A Tabela 1 mostra os resultados da síntese como potência, área e slack.

Tabela 1 – Relatório de Área e Potência

| Área $(nm^2)$   | Área Combinacional                  | 815,360  |

|-----------------|-------------------------------------|----------|

|                 | Área Sequencial                     | 561,971  |

|                 | Área Buffer/Inverter                | 75,264   |

|                 | Área da Célula                      | 1532,877 |

|                 | Área dos Fios                       | 1159,907 |

|                 | Área Total                          | 2692,784 |

| Power $(\mu W)$ | Potência Interna da Célula          | 60,505   |

|                 | Potência Consumida na Troca de Fios | 47,218   |

|                 | Potência Dissipada na Célula        | 0,022    |

|                 | Potência Total                      | 107,746  |

| Slack (ps)      | Delay do Pior Caminho               | 158      |

Fonte: Autoria própria.

## 4.2 Resultados e Cobertura Funcional

Para realizar a análise dos testes do *scoreboard*, foram gerados arquivos de *report* para os três testes mencionados na Seção 3.2.4. Já para a cobertura funcional, usou-se uma *seed* de valor 125 e foi realizada uma sequência de 1000 transações para estimular o *design*. Para as métricas de cobertura, utilizou-se a ferramenta Integrated Metrics Center<sup>TM</sup>. A Tabela 2 mostra a quantidade de *matches* e *mismatches* de cada teste e a Figura 12 mostra as métricas de cobertura funcional.

Tabela 2 – Tabela de Testes

| Testes     | Condição de Início | Leitura/Escrita | Condição de Parada |

|------------|--------------------|-----------------|--------------------|

| Matches    | 999                | 970             | 998                |

| Mismatches | 0                  | 29              | 1                  |

Fonte: Autoria própria.

Verification Hierarchy 🗗 🕳 📰 Details Verification Metrics Overall Average Grade Overall Covered Assertion Status Grade \* Metrics Attributes Ex UNR Name Overall Average Grade 🕏 ■ Verification Metrics 94.33% 387 / 425 (9. 94.33 ■ Overall Types 95.14% 261 / 280 (9... 93.52 uvm\_pkg 0 / 0 (n/a) ₩ Block 92.57 🗸 💶 i2c\_pkg 100% 135 / 135 (1... Statement ▲ Page 12c\_subscriber::i2c\_cg 100% 135 / 135 (1... Expression **1** 100% 100% 1 / 1 (100%) ₽ start cp ₩ Toggle 91.56 **1** 100% 1 / 1 (100%) scl start cp 100% 64 / 64 (100%) addr cp ■ Functional **1** 100% 🚇 rw\_logic\_cp 2 / 2 (100%) Assertion **1**00% 64 / 64 (100%) ₽ w\_data\_cp CoverGroup **1**00% 🖺 ack\_data\_cp **1** 100% 1 / 1 (100%) n/a FaultNode **1**00% 1 / 1 (100%) <u>□</u> stop\_cp n/a **2** 100% 1 / 1 (100%) 🚇 scl\_stop\_cp n/a top\_pkg 0 / 0 (n/a) 1 top **1** 100% 8 / 8 (100%) 1 i2c\_interface 90.91% 20 / 22 (90.9... 1 i2c\_master 89.64% 98 / 115 (85.... Instances 93.52% 126 / 145 (8... ▶ **1** uvm\_pkg 0 / 0 (n/a) n/a i2c\_pkg 0 / 0 (n/a) top\_pkg 0/0(n/a) **>** -1 top 93.52% 126 / 145 (8... Showing 22 items Showing 11 items

Figura 12 – Métricas de Cobertura

Fonte: Autoria própria.

A partir dos dados acima, pode-se concluir que a verificação do bloco foi bem sucedida, atingindo uma métrica de cobertura funcional de 100% e uma porcentagem de mismatches de aproximadamente 1%.

## 5 Conclusões

Esse trabalho teve como objetivo a concepção de um  $design\ digital$  de um controlador  $I^2C$ , bem como a sua verificação funcional utilizando a metodologia UVM.

Foi feito o estudo da especificação do protocolo  $I^2C$  e identificado suas funcionalidades básicas e essenciais. A partir disso montou-se um enlace de comunicação básico entre um controlador e um alvo para o teste das funcionalidades tidas como primordiais.

A partir disso, foi feito o *design* digital e desenvolvido um ambiente de verificação que agisse conforme um alvo, a fim de estimular o bloco do controlador. Com os resultados da simulação, foi possível identificar o bom funcionamento do bloco controlador e com as métricas obtidas na verificação funcional, foi constatado o seu funcionamento coerente.

Além disso, foi feita a síntese lógica do bloco, obtendo-se informações relativas a área, potência e *performance* do bloco. Com isso, é dado o primeiro passo para a confecção e projeto de um chip ASIC.

Como trabalhos e melhorias futuras, pode-se elencar alguns tópicos:

- Expandir as funcionalidades do design digital para lidar com um barramento com mais de um alvo e controlador, criando as lógicas necessária para o controle do barramento.

- Aumentar a quantidade de features do barramento, tais como clock synchronization and stretching, modos rápido e ultra-rápidos de operação, 10-bit adrressing, entre outros.

- Resolver os problemas relacionados ao sincronismo de byte implementando um gerador de frequência para linha SCL do barramento  $I^2C$ .

- Aumentar a quantidade de dados possíveis de serem enviados em uma única transmissão.

- Fazer uma funcionalidade para o controlodar lidar com o n\u00e3o reconhecimento do alvo e criar m\u00e9todos que garantam a entrega do dado.

## Referências Bibliográficas

CHAUHAN, K. Asic design flow in vlsi engineering services (a quick guide). *eInfoChips*, 2020. Citado na página 5.

FATHY, K.; SALAH, K.; GUINDI, R. A proposed methodology to improve uvm-based test generation and coverage closure. In: 2015 10th International Design Test Symposium (IDT). [S.l.: s.n.], 2015. p. 147–148. Citado na página 8.

FOSTER, H. 2020 wilson research group functional verification study. In: . [s.n.], 2020. Disponível em: <https://blogs.sw.siemens.com/verificationhorizons/2020/11/05/part-1-the-2020-wilson-research-group-functional-verification-study/>. Citado 2 vezes nas páginas 7 e 9.

HOLLINGWORTH, P. Logic synthesis. In: [Proceedings] EURO ASIC '90. [S.l.: s.n.], 1990. p. 250–256. Citado na página 5.

INITIATIVE, A. S. Universal Verification Methodology (UVM) 1.2 User's Guide. 2.0. ed. [S.l.], 2015. Disponível em: <a href="https://www.accellera.org/images/downloads/standards/uvm/uvm\_users\_guide\_1.2.pdf">https://www.accellera.org/images/downloads/standards/uvm/uvm\_users\_guide\_1.2.pdf</a>. Citado 3 vezes nas páginas 9, 10 e 12.

KAITH, D.; PATEL, J. B.; GUPTA, N. An introduction to functional verification of i2c protocol using uvm. *International Journal of Computer Applications*, Foundation of Computer Science, v. 121, n. 13, 2015. Citado na página 14.

KUMAR, T. T.; GOPINATH, C. Verification of i2c master core using system verilog uvm. *International Journal of Science and Research (IJSR)*, v. 5, n. 1, p. 641–645, 2016. Citado na página 7.

MARTIN, K. Digital Integrated Circuit Design. second. [S.l.]: Oxford University Press, 2002. Citado na página 4.

SALAH, K. A uvm-based smart functional verification platform: Concepts, pros, cons, and opportunities. In: 2014 9th International Design and Test Symposium (IDT). [S.l.: s.n.], 2014. p. 94–99. Citado na página 8.

SEMICONDUCTOR, N.  $I^2C$ -bus specification and user manual. 7.0. ed. [S.1.], 2021. Disponível em: <a href="https://www.nxp.com/docs/en/user-guide/UM10204.pdf">https://www.nxp.com/docs/en/user-guide/UM10204.pdf</a>>. Citado 7 vezes nas páginas 1, 13, 14, 15, 16, 26 e 29.

SUTHERLAND, S.; DAVIDMANN, S.; FLAKE, P. SystemVerilog for Design: A Guide to using SystemVerilog for Hardware Design and Modeling. second. [S.l.]: Springer Science Business Media, 2006. Citado na página 6.

VIJAYARAGHAVAN, S.; RAMANATHAN, M. A practical guide for System Verilog assertions. first. [S.l.]: Springer Science Business Media, 2005. Citado na página 6.

# ANEXO A – Códigos do Ambiente de Verificação *UVM* em *SystemVerilog*

Neste apêndice é apresentado os códigos para a implementação dos módulos utilizados no ambiente de verificação *UVM*, em linguagem de descrição de *hardware SystemVerilog*.

• Top:

```

`include "i2c master.sv"

3 module top;

import uvm_pkg::*;

5

import i2c_pkg::*;

import top_pkg::*;

bit clk;

9

bit reset;

10

11

i2c_interface i2c_if(.clk(clk), .reset(reset));

12

i2c_master mst(i2c_if);

13

14

initial begin

clk = 1;

16

reset = 0;

17

#10ns reset = 1;

#10ns reset = 0;

19

end

20

21

22

always #10ns clk = !clk;

23

initial begin

24

uvm_config_db#(virtual i2c_interface)::set(uvm_root::get(),...

25

"*", "vif", i2c_if);

run_test("my_test");

26

27

end

endmodule

```

• Top Package e I<sup>2</sup>C Package:

```

package top_pkg;

include "uvm_macros.svh"

import uvm_pkg::*;

import i2c_pkg::*;

include "../tb/my_env.sv"

include "../tb/my_test.sv"

endpackage

```

```

`ifndef I2C_PKG

define I2C_PKG

2

timescale 1 ns/1 ps

5

6 package i2c_pkg;

`include "uvm_macros.svh"

import uvm_pkg::*;

8

9

`include "../src/i2c_sequence_item.svh"

10

`include "../src/i2c_sequence.svh"

11

12

`include "../src/i2c_sequencer.svh"

`include "../src/i2c_driver.svh"

13

`include "../src/i2c_monitor.svh"

14

`include "../src/i2c_agent.svh"

15

`include "../src/i2c_sb_subscriber.svh"

16

`include "../src/i2c_scoreboard.svh"

17

`include "../src/i2c_subscriber.svh"

18

19

endpackage

20

21

`endif//I2C_PKG

```

• Test:

```

class my_test extends uvm_test;

`uvm_component_utils(my_test)

i2c_sequence seq;

my_env env;

//int cycles = 10;

function new(string name, uvm_component parent = null);

super.new(name, parent);

```

```

endfunction

10

11

function void build_phase(uvm_phase phase);

12

super.build_phase(phase);

13

seq = i2c_sequence::type_id::create("seq", this);

14

env = my_env::type_id::create("env", this);

16

endfunction

17

task main_phase(uvm_phase phase);

18

phase.raise_objection(this);

19

seq.start(env.i2c_agt.sqr);

20

phase.drop_objection(this);

21

endtask

22

23

24 endclass

```

#### • Environment:

```

class my_env extends uvm_env;

2

`uvm_component_utils(my_env)

3

i2c_agent

i2c_agt;

i2c_subscriber

5

i2c_sub;

i2c scoreboard

i2c sb;

function new(string name, uvm_component parent = null);

9

super.new(name, parent);

10

endfunction

11

12

virtual function void build_phase(uvm_phase phase);

13

super.build_phase(phase);

14

i2c\_agt = i2c\_agent::type\_id::create("i2c\_agt", this);

i2c_sub = i2c_subscriber::type_id::create("i2c_sub", this);

i2c_sb = i2c_scoreboard::type_id::create("i2c_sb", this);

17

endfunction

18

19

virtual function void connect_phase(uvm_phase phase);

20

super.connect_phase(phase);

21

22

i2c_agt.mon_ap.connect(i2c_sub.analysis_export);

i2c_agt.mon_ap.connect(i2c_sb.i2c_analysis_export);

23

endfunction

24

endclass

```

• Scoreboard:

```

class i2c_scoreboard extends uvm_scoreboard;

`uvm_component_utils(i2c_scoreboard)

2

3

uvm analysis export#(i2c sequence item) i2c analysis export;

4

local i2c_sb_subscriber i2c_sb_sub;

int count_match_start;

6

int count mismatch start;

7

int count_match_rw;

8

int count_mismatch_rw;

9

int count match stop;

int count_mismatch_stop;

11

12

function new(string name, uvm_component parent);

13

super.new(name, parent);

14

endfunction: new

15

function void build_phase(uvm_phase phase);

17

super.build_phase(phase);

18

i2c_analysis_export = new( .name("i2c_analysis_export"), ....

19

parent(this));

i2c_sb_sub = i2c_sb_subscriber::type_id::create(.name("...

i2c_sb_sub"), .parent(this));

count_match_start = 0;

21

22

count mismatch start = 0;

23

count_match_rw = 0;

count_mismatch_rw = 0;

24

25

count_match_stop = 0;

26

count_mismatch_stop = 0;

endfunction: build_phase

27

28

function void connect_phase(uvm_phase phase);

29

super.connect phase(phase);

30

i2c_analysis_export.connect(i2c_sb_sub.analysis_export);

31

32

endfunction: connect_phase

33

34

virtual function void check_i2c_start(i2c_sequence_item i2c_tx);

35

36

uvm_table_printer p = new;

37

int f_start = 0;

38

f_start = $fopen("./start_condition.txt", "a");

39

40

if (i2c_tx.start = 0 \&\& i2c_tx.scl_start = 1) begin

41

`uvm_info("i2c_scoreboard",

42

{ "Start condition passed.\n", i2c_tx.sprint...

43

(p) }, UVM_LOW);

count_match_start++;

44

```

```

if (f start) begin

45

$fwrite(f_start, "i2c_scoreboard \n Start condition ...

46

passed.\langle n"\rangle;

$fwrite(f_start, "Matches: %d", count_match_start);

47

end else begin

48

49

`uvm_error("i2c_scoreboard", {"Failed to open file: ...

start_condition.txt" });

end

50

end else begin

51

`uvm_error("i2c_scoreboard",

52

{ "Start condition failed.\n", i2c_tx....

sprint(p) });

54

count_mismatch_start++;

if (f_start) begin

$fwrite(f_start, "i2c_scoreboard \n Start condition ...

56

failed . \ n");

$fwrite(f_start, "Mismatches: %d", count_mismatch_start...

57

);

end else begin

58

`uvm_error("i2c_scoreboard", {"Failed to open file: ...

59

start_condition.txt" });

end

60

end

61

62

close_file(f_start);

63

64

endfunction: check_i2c_start

65

66

67

68

69

virtual function void check_i2c_rw(i2c_sequence_item i2c_tx);

int count = 0;

70

int f_rw = 0;

71

uvm_table_printer p = new;

72

f_rw = $fopen("./rw_check.txt", "a");

73

74

if (i2c_tx.rw_logic == 1) begin

75

if(i2c_tx.ack_data == 1) begin

76

`uvm_info("i2c_scoreboard",

{ "Read operation passed.\n", i2c_tx.sprint(...

78

p) }, UVM_LOW);

count_match_rw++;

79

if (f rw) begin

80

$fwrite(f_rw, "i2c_scoreboard \n Read operation ...

81

passed.\langle n"\rangle;

$fwrite(f_rw, "Matches: %d", count_match_rw);

82

end else begin

83

```

```

`uvm_error("i2c_scoreboard", {"Failed to open file:...

84

rw_check.txt" });

end

85

end else begin

86

`uvm_error("i2c_scoreboard",

87

88

{ "Read operation failed.\n", i2c_tx.sprint...

(p) });

count_mismatch_rw++;

89

if (f_rw) begin

90

$fwrite(f rw, "i2c scoreboard \n Read operation ...

91

failed . \ n");

$fwrite(f_rw, "Mismatches: %d", count_mismatch_rw);

92

end else begin

93

`uvm_error("i2c_scoreboard", {"Failed to open file:...

94

rw_check.txt"});

end

95

end

96

end else begin

97

foreach (i2c_tx.w_data[i]) begin

98

if (i2c_tx.recovery_w_data[i] == i2c_tx.w_data[i]) count...

99

++;

end

100

if (count == 8) begin

`uvm_info("i2c_scoreboard",

102

{ "Write operation passed.\n", i2c_tx.sprint...

103

(p) }, UVM_LOW);

count_match_rw++;

104

if (f_rw) begin

105

fwrite(f_rw, "i2c_scoreboard \n Write operation ...

106

passed.\langle n'' \rangle;

107

$fwrite(f_rw, "Matches: %d", count_match_rw);

108

end else begin

`uvm_error("i2c_scoreboard", {"Failed to open file:...

109

rw_check.txt"});

end

110

end else begin

111

`uvm_error("i2c_scoreboard",

112

{ "Write operation failed.\n", i2c_tx....

113

sprint(p) \});

count\_mismatch\_rw++;

114

if (f rw) begin

115

$fwrite(f_rw, "i2c_scoreboard \n Write operation ...

116

failed . \ n");

$fwrite(f rw, "Mismatches: %d", count mismatch rw);

117

end else begin

118

`uvm_error("i2c_scoreboard", {"Failed to open file:...

119

rw_check.txt"});

```

```

end

120

121

end

end

122

123

close_file(f_rw);

124

125

endfunction: check_i2c_rw

126

127

virtual function void check_i2c_stop(i2c_sequence_item i2c_tx);

128

uvm_table_printer p = new;

129

int f_stop = 0;

130

f_stop = $fopen("./stop_condition.txt", "a");

131

132

if (i2c_tx.stop = 1 \&\& i2c_tx.scl_stop = 1) begin

133

`uvm_info("i2c_scoreboard",

134

{ "Stop condition passed.\n", i2c_tx.sprint(...

135

p) }, UVM_LOW);

count_match_stop++;

136

if (f_stop) begin

137

$fwrite(f_stop, "i2c_scoreboard \n Stop condition ...

138

passed.\langle n"\rangle;

$fwrite(f_stop, "Matches: %d", count_match_stop);

139

end else begin

`uvm_error("i2c_scoreboard", {"Failed to open file: ...

141

stop_condition.txt"});

end

142

end else begin

143

`uvm_error("i2c_scoreboard",

144

{ "Stop condition failed.\n", i2c_tx.sprint...

145

(p) });

146

count_mismatch_stop++;

if (f_stop) begin

147

$fwrite(f_stop, "i2c_scoreboard \n Stop condition ...

148

failed.\n");

$fwrite(f_stop, "Mismatches: %d", count_mismatch_stop);

149

end else begin

150

`uvm_error("i2c_scoreboard", {"Failed to open file: ...

151

stop condition.txt" );

end

152

end

153

154

close_file(f_stop);

155

156

endfunction: check i2c stop

157

158

159

160 // Fun o para fechar o arquivo

```

#### • Subscriber:

```

class i2c_subscriber extends uvm_subscriber#(i2c_sequence_item);

`uvm_component_utils(i2c_subscriber)

2

3

i2c_sequence_item tr;

covergroup i2c_cg;

coverpoint tr.start {bins str_null = {0};}

start_cp:

coverpoint tr.scl_start {bins str_scl_true ...

scl_start_cp:

= \{1\};\}

coverpoint tr.addr;

addr_cp:

9

rw_logic_cp:

coverpoint tr.rw_logic;

10

coverpoint tr.w_data;

w_data_cp:

11

ack_data_cp:

coverpoint tr.ack_data {bins ack_true = ...

12

\{1\};\}

stop_cp:

coverpoint tr.stop {bins stp_true = {1};}

13

scl_stop_cp:

coverpoint tr.scl_start {bins stp_scl_true ...

14